Синтез и анализ последовательных схем (синтез счетчиков)

Министерство

науки и образования Украины

Национальный

аэрокосмический университет им. Н.Е. Жуковского

«Харьковский

авиационный институт»

Кафедра

501

«Проектирование

радиоэлектронных систем летательных аппаратов»

Лабораторная

работа

«Синтез

и анализ последовательных схем (синтез счетчиков)»

Выполнил: студент 526

группы Момот О. А.

Проверил: к.т.н., доцент

Мазуренко А.В.

г.

Харьков

Введение

Цель работы: закрепить знания по

синтезу последовательных схем (счетчиков), построить логическую схему счетчика

в среде Max+Plus II с использованием редактора символов и смоделировать ее

работу с помощью эмулятора работы логических схем.

Теоретическая часть

Схема, выходные сигналы которой

зависят не только от текущих значений входных сигналов, но и от

последовательности значений входных сигналов в прошлом, называется

последовательной схемой или схемой с памятью.

Триггер - это устройство

последовательностного типа с двумя устойчивыми состояниями равновесия,

предназначенное для записи и хранения информации. Под действием входных

сигналов триггер может переключаться из одного устойчивого состояния в другое.

При этом напряжение на его выходе скачкообразно изменяется.

Классификация

Триггеры подразделяются на две

большие группы - динамические и статические. Названы они так по способу

представления выходной информации.

Динамический триггер представляет

собой управляемый генератор, одно из состояний которого (единичное)

характеризуется наличием на выходе непрерывной последовательности импульсов

определённой частоты, а другое (нулевое) - отсутствием выходных импульсов.

Смена состояний производится внешними импульсами (рис. 3). Динамические

триггеры в настоящее время используются редко.

К статическим триггерам относят

устройства, каждое состояние которых характеризуется неизменными уровнями

выходного напряжения (выходными потенциалами): высоким - близким к напряжению

питания и низким - около нуля. Статические триггеры по способу представления

выходной информации часто называют потенциальными.

Статические (потенциальные)

триггеры, в свою очередь, подразделяются на две неравные по практическому

значению группы - симметричные и несимметричные триггеры. Оба класса

реализуются на двухкаскадном двухинверторном усилителе с положительной обратной

связью, а названием своим они обязаны способам организации внутренних

электрических связей между элементами схемы.

Симметричные статические триггеры

составляют основную массу триггеров, используемых в современной

радиоэлектронной аппаратуре. Схемы симметричных триггеров в простейшей

реализации (2х2ИЛИНЕ) показаны на рис. 4.

Основной и наиболее общий

классификационный признак - функциональный - позволяет систематизировать

статические симметричные триггеры по способу организации логических связей

между входами и выходами триггера в определённые дискретные моменты времени до

и после появления входных сигналов. По этой классификации триггеры

характеризуются числом логических входов и их функциональным назначением (рис.

5).

Вторая классификационная схема,

независимая от функциональной, характеризует триггеры по способу ввода

информации и оценивает их по времени обновления выходной информации

относительно момента смены информации на входах (рис. 6).

Каждая из систем классификации

характеризует триггеры по разным показателям и поэтому дополняет одна другую. К

примеру, триггеры RS-типа могут быть в синхронном и асинхронном исполнении.

Асинхронный триггер изменяет своё

состояние непосредственно в момент появления соответствующего информационного

сигнала(ов), с некоторой задержкой равной сумме задержек на элементах, составляющих

данный триггер.

Синхронные триггеры реагируют на

информационные сигналы только при наличии соответствующего сигнала на так

называемом входе синхронизации С (от англ. clock). Этот вход также обозначают

термином «такт». Такие информационные сигналы называют синхронными. Синхронные

триггеры в свою очередь подразделяют на триггеры со статическим и с

динамическим управлением по входу синхронизации С.

Триггеры со статическим управлением

воспринимают информационные сигналы при подаче на вход С логической единицы

(прямой вход) или логического нуля (инверсный вход).

Триггеры с динамическим управлением

воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С

от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический

С-вход). Также встречается название «триггер управляемый фронтом».

Одноступенчатые триггеры (latch,

защёлки) состоят из одной ступени представляющей собой элемент памяти и схему

управления, бывают, как правило, со статическим управлением. Одноступенчатые

триггеры с динамическим управлением применяются в первой ступени

двухступенчатых триггеров с динамическим управлением. Одноступенчатый триггер

на УГО обозначают одной буквой - Т.

Двухступенчатые триггеры (flip-flop,

шлёпающие) делятся на триггеры со статическим управлением и триггеры с

динамическим управлением. При одном уровне сигнала на входе С информация, в

соответствии с логикой работы триггера, записывается в первую ступень (вторая

ступень заблокирована для записи). При другом уровне этого сигнала происходит копирование

состояния первой ступени во вторую (первая ступень заблокирована для записи),

выходной сигнал появляется в этот момент времени с задержкой равной задержке

срабатывания ступени. Обычно двухступенчатые триггеры применяются в схемах, где

логические функции входов триггера зависят от его выходов, во избежание

временны́х гонок. Двухступенчатый

триггер на УГО обозначают двумя буквами - ТТ.

Триггеры со сложной логикой бывают

также одно- и двухступенчатые. В этих триггерах наряду с синхронными сигналами присутствуют

и асинхронные. Такой триггер изображён на рис. 1, верхний (S) и нижний (R)

входные сигналы являются асинхронными.

Триггерные схемы классифицируют

также по следующим признакам:

числу целочисленных устойчивых

состояний (основанию системы счисления) (обычно устойчивых состояний два, реже

- больше, см. двоичный триггер, троичный триггер, четверичный триггер[8], …,

десятичный триггер, …, n-ичный триггер, …);

числу уровней - два уровня (высокий,

низкий) в двухуровневых элементах, три уровня (положительный, ноль,

отрицательный) в трёхуровневых элементах[9], …, N-уровней в N-уровневых

элементах, …;

по способу реакции на помехи -

прозрачные и непрозрачные. Непрозрачные, в свою очередь, делятся на проницаемые

и непроницаемые.

по составу логических элементов

(триггеры на элементах И-НЕ, ИЛИ-НЕ и др.).

Счётчик числа импульсов -

устройство, на выходах которого получается двоичный (двоично-десятичный) код,

определяемый числом поступивших импульсов. Счётчики могут строиться на

двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Основной параметр счётчика - модуль

счёта - максимальное число единичных сигналов, которое может быть сосчитано

счётчиком. Счётчики обозначают через СТ (от англ. counter).

Классификация

Счётчики классифицируют:

на двоичных триггерах

на троичных триггерах[1]

на n-ичных триггерах

по модулю счёта:

двоично-десятичные (декада);

двоичные;

с произвольным постоянным модулем

счёта;

с переменным модулем счёта;

по направлению счёта:

суммирующие;

вычитающие;

реверсивные;

по способу формирования внутренних

связей:

с последовательным переносом;

с ускоренным переносом;

с параллельным ускоренным переносом;

со сквозным ускоренным переносом;

с комбинированным переносом;

кольцевые;

по способу переключения триггера:

асинхронные;

Счётчик Джонсона.

Алгоритм синтеза счетчиков не

кратным 2n

Могут быть получены из счетчиков

кратным степени 2n путем исключения некоторых двоичных комбинаций.

Определяется ближайшее к заданному

коэффициенту пересчета число М = 2n >= Kпер. зад.

Определяется число каскадов или

триггеров n = log2M счетчика кратным 2n.

Строится схема счетчика с

коэффициенту пересчета равным степени 2n.

На выходах счетчика записывается

двоичная комбинация требуемого коефициента пересчета. Второй вариант: на входах

предварительной установки триггеров записывается двоичный код числа S = M -

Kпер. зад.

Те выходы на которых записаны

единицы обьеденяются с инверсным значением выходов на которых записаны нули

двоичного кода схемой «и» выход который через схему «или» подключается к входам

«reset» всех триггеров. Второй вариант: с выхода переноса сигнал подается на те

входы предварительной установки триггеров на которых устанавливается «1».

синтез счетчик логический триггер

Задание

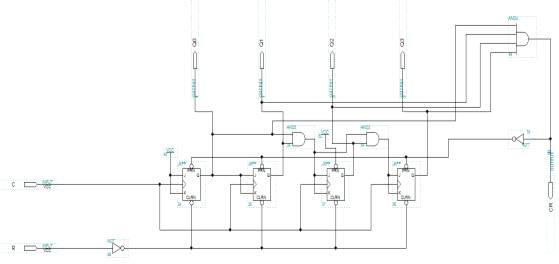

Построить схему суммирующего счетчика

с параллельным переносом с коэффициентом пересчета Kпер. зад. = 11 на основе JK

- триггеров.

Выполнение задания= 16; Kпер. зад. =

11;= 4;пер. зад. = Qi(2) = 1011(2) = 11(11)

Рисунок 1 Логическая

схема

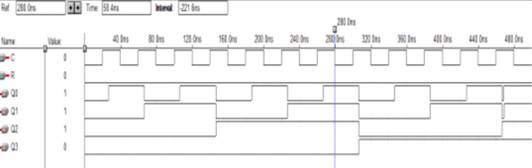

Рисунок 2 Результат

моделирования (Временная диаграмма)