Разработка микропроцессорной системы управления объектом

Содержание

Введение

.

Разработка структурной схемы

.

Краткое описание элементов схемы

.

Описание электрической принципиальной схемы

.

Блок схема алгоритма и программа

.

Карты распределения адресного пространства памяти и увв

.

Оценка ёмкости ПЗУ и ОЗУ

.

Расчет потребления тока

Заключение

Список

литературы

ПРИЛОЖЕНИЕ

1. Структурная схема МПС

ПРИЛОЖЕНИЕ

2. Листинг программы

ВВЕДЕНИЕ

К настоящему времени ЭВМ используются во всех

сферах человеческой деятельности. Важную роль при этом сыграло развитие микроэлектроники:

создание больших интегральных схем микропроцессоров, запоминающих устройств и

др. Микропроцессорной технике здесь отводится особое место, поскольку

микропроцессоры обладают высокими функциональными возможностями и

эксплуатационными характеристиками.

БИС, на которых построены современные МПС,

сочетают в себе высокую степень интеграции, обеспечивающую большие

функциональные возможности, с универсальностью по применению.

Универсальность достигается тем, что в

микропроцессорных БИС реализованы сложные устройства, позволяющие выполнять над

исходными данными логические и арифметические операции, при этом управление

ходом вычисления позволяется вести программно. Все современные мини-ЭВМ

построены с использованием БИС, входящих в различные МП комплекты. Под

микропроцессорными БИС понимают совокупность МП и других интегральных

микросхем, совместимых по технологическому и конструкторскому исполнению и

предназначенных для совместного использования при построении различных средств

ВТ.

Основой каждого МПК БИС

является микропроцессор (МП) - программно управляемое устройство для обработки

данных. При использовании МП необходимо ясно представлять динамику его работы,

т.е., на каких магистралях в зависимости от каких управляющих сигналов и какого

МП будут выдаваться та или иная информация. Это поможет понять работу схемы,

согласовать ее с различными периферийными устройствами.

В данном курсовом проекте

рассматривается система, построенная на универсальном МПК БИС серии К580,

который являлся в свое время наиболее распространенным. Широкое использование

комплекта обуславливалось функциональной законченностью.

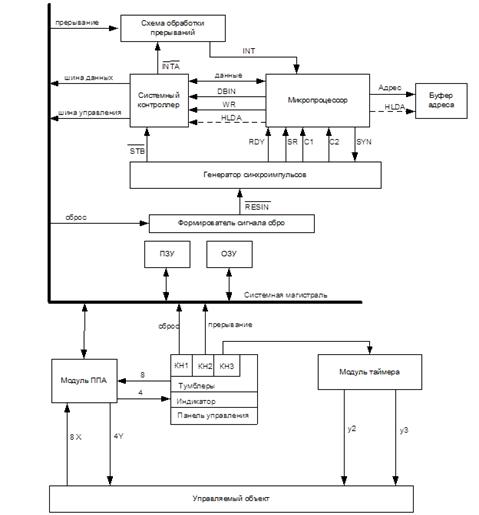

1. Разработка структурной схемы

Структурная схема устройства разрабатывается на

основании анализа технического задания.

В структуру разрабатываемой МПС

необходимо включить генератор тактовых импульсов (генератор), снабжает

остальные блоки синхросигналами, вырабатывает импульсы синхронизации С1 и С2 с

уровнем 12В, а также сигнал  . Наряду с генератором мы должны

включить управляемый интегральный таймер (ИТ), предназначенный для отсчета

временных интервалов при выработке сигналов Y2 и Y3.Тактирование

таймера осуществляется от генератора. Основной частью устройства будет

микропроцессор, который является основным активным компонентом системы. Для

работы с внешними устройствами надо использовать параллельный периферийный

адаптер. Для организации системной(общей) шины для обмена данных и корректного

функционирования МПС следует использовать усилители формирователи, т.к. они

только способствуют усилению сигнала, то их на структурной схеме отображать не

будем. Для формирования временных интервалов для управления внешним устройством

используем интегральный управляемый таймер, который передает сигналы Y2 и Y3.

Программа, которая регулирует работу МПС хранится в ПЗУ. ОЗУ используется для

того чтобы связаться с ППА и передавать данные на объект управления, а также

для получения ответных сигналов от управляемого объекта. Схему обработки

прерываний организуем тоже на усилителе, записав код вектора прерывания. С

учетом изложенного структурную схему устройства можно представить в виде,

представленном на рис.1.1.

. Наряду с генератором мы должны

включить управляемый интегральный таймер (ИТ), предназначенный для отсчета

временных интервалов при выработке сигналов Y2 и Y3.Тактирование

таймера осуществляется от генератора. Основной частью устройства будет

микропроцессор, который является основным активным компонентом системы. Для

работы с внешними устройствами надо использовать параллельный периферийный

адаптер. Для организации системной(общей) шины для обмена данных и корректного

функционирования МПС следует использовать усилители формирователи, т.к. они

только способствуют усилению сигнала, то их на структурной схеме отображать не

будем. Для формирования временных интервалов для управления внешним устройством

используем интегральный управляемый таймер, который передает сигналы Y2 и Y3.

Программа, которая регулирует работу МПС хранится в ПЗУ. ОЗУ используется для

того чтобы связаться с ППА и передавать данные на объект управления, а также

для получения ответных сигналов от управляемого объекта. Схему обработки

прерываний организуем тоже на усилителе, записав код вектора прерывания. С

учетом изложенного структурную схему устройства можно представить в виде,

представленном на рис.1.1.

Взаимодействие микропроцессора с

памятью и средствами ВВ осуществляется посредством интерфейса "Общая

шина", состоящего из нескольких десятков линий (число линий в шине

называют ее шириной).

Рис. 1.1 Структурная схема МПС

Взаимообмен между МП, памятью и периферийными

устройствами производится в режиме разделения времени (временного

мультиплексирования). Для этого устройства, не участвующие в обмене,

переводятся в режим высокого выходного сопротивления. Этим достигается

отключение их от системных шин.

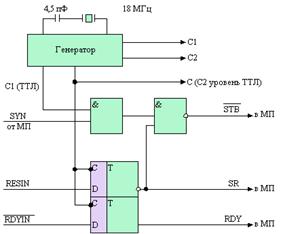

В структуру разрабатываемого

устройства необходимо включить генератор тактовых импульсов (генератор). Схема

БИС генератора синхроимпульсов (ГСИ) КР580ГФ24 приведена на рис.1.2. ГСИ

вырабатывает импульсы синхронизации микропроцессора С1 и С2 с уровнем 12 В,

сигнал С с уровнем ТТЛ, а также сигнал  , стробирующий слово состояния микропроцессора.

Кроме того, в БИС размещены схемы, обеспечивающие синхронизацию выдачи в

микропроцессор сигналов сброса и готовности.

, стробирующий слово состояния микропроцессора.

Кроме того, в БИС размещены схемы, обеспечивающие синхронизацию выдачи в

микропроцессор сигналов сброса и готовности.

Основой МПС является микропроцессор

(МП) КР580ВМ80А, работающий с тактовой частотой 2 МГц. Параллельный интерфейс

МПС с внешними устройствами обеспечивается параллельным периферийным адаптером

(ППА) КР580ВВ55, а временные интервалы формируются программируемым таймером

КР580ВИ53.

Рис. 1.2 Схема генератора

синхроимпульсов КР580ГФ24

Формирователь сигнала сброса служит

для начальной установки МПС при включении питания или при нажатии кнопки КН1.

Системный контролер (СК) служит для

выработки системных управляющих сигналов на основе слова состояния

микропроцессора, выдаваемого по шине данных.

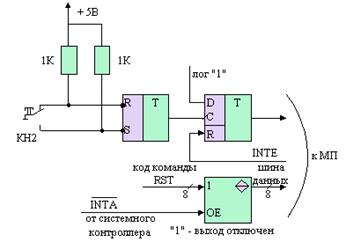

Для осуществления прерываний в МПМ

могут использоваться различные аппаратные средства, в частности в схеме. Первый

триггер служит для предотвращения "дребезга" контактов кнопки КН2,

второй - для выдачи запроса на прерывание в микропроцессор. После поступления

от микропроцессора подтверждения запроса на прерывание на шину данных

микропроцессора подается код команды RST, соответствующей реализуемому уровню

прерывания.

Генератор - тактовый генератор,

предназначенный для формирования тактовых импульсов с заданной частотой;

МП модуль - микропроцессор (МП)

КР580ВМ80А, работающий с тактовой частотой 2 МГц;

Тумблеры - восемь тумблеров,

определяющих значение константы К, используемой при реализации алгоритма работы

МПС;

Кнопка КН1 "Сброс",

осуществляющую начальную установку и запуск МПС;

Кнопки КН2 и КН3, обеспечивающие

управление выдачей сигналов y2 и y3;

Модуль таймера - на базе БИС программируемого

таймера (ПТ) КР580ВИ53;

Модуль ППА - модуль периферийного параллельного

адаптера КР580ВВ55;

ПЗУ - постоянное запоминающее устройство на

К155РЕ3;

ОЗУ - оперативное запоминающее устройство на

К155РУ2.

Рис. 1.3 Устройство вв/выв. пульт

контроля и управления

В ЗУ хранятся программы и данные. В

современных ЭВМ ЗУ выполняют многоуровневым: ВЗУ (диски, ленты, барабаны); ОЗУ

(полупроводниковые ОЗУ, феритные сердечники, цилиндрических магнитных доменах

ИМД); СОЗУ (роны, КЭШ-память и др.).

Процессор предназначен для обработки

информации.

Данные на обработку поступают из

ОЗУ. Обрабатываются по программе, которая так же размещается в ОЗУ. Процесс

обработки происходит в центре, состоящем из оперативной памяти (СОЗУ, ОЗУ) и

процессора.

Процессор делит на 2 части:

управляющий автомат чаще называют УУ и АЛУ устройство управление (управляющий

автомат), и (оперативное устройство) арифметико-логическим устройством (АЛУ).

УВВ предназначено для ввода программ

и данных в оперативную память то есть данные в начале подготавливаются в виде

ПФК, ПФЛ, магнитных лент, магнитных дисков, а затем вводятся в ОП машины.

Только после этого программа запускается на обработку. В современных машинах

диалогового данные в память заносятся непосредственно с экрана дисплея.

Пульт контроля и управления

предназначен для ручного пуска различного рода тестовых программ, контроля хода

вычислительного процесса или функционирования устройства ЭВМ.

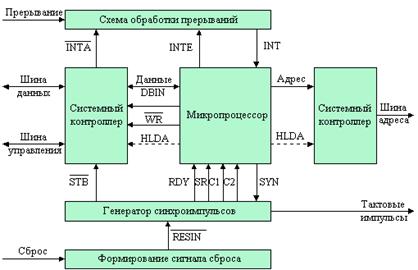

Микропроцессорный модуль (МПМ)

является основной частью МПС и управляет всеми остальными ее блоками.

Обобщенная структура МПМ показана на рис.1.4. МПМ содержит:

· микропроцессор КР580ВМ80А;

· системный контроллер;

· генератор синхроимпульсов;

· формирователь сигнала сброса;

· схему обработки прерываний;

· буфер адреса.

Рис. 1.4 Обобщенная структура микропроцессорного

модуля МПС

Формирователь сигнала сброса (рис.1.5) служит

для начальной установки МПС при включении питания или при нажатии кнопки КН1.

Время заряда конденсатора через резистор определяет длительность формируемого

импульса. Диод служит для быстрой разрядки конденсатора при кратковременном

отключении питания.

Схема БИС генератора синхроимпульсов

(ГСИ) КР580ГФ24 приведена на рис.1.2. ГСИ вырабатывает импульсы синхронизации

микропроцессора С1 и С2 с уровнем 12 В, сигнал С с уровнем ТТЛ, а также сигнал  ,

стробирующий слово состояния микропроцессора. Кроме того, в БИС размещены

схемы, обеспечивающие синхронизацию выдачи в микропроцессор сигналов сброса и

готовности.

,

стробирующий слово состояния микропроцессора. Кроме того, в БИС размещены

схемы, обеспечивающие синхронизацию выдачи в микропроцессор сигналов сброса и

готовности.

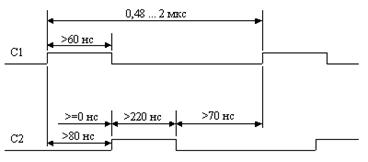

Вырабатываемые синхроимпульсы должны

соответствовать требованиям, задаваемым рис.1.6.

Рис. 1.5 Формирование импульса

сброса

Рис. 1.6 Требования к параметрам сигналов

синхронизации МП КР580ВМ80А

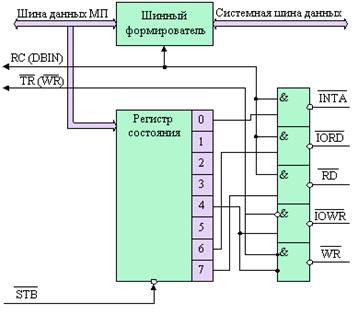

Системный контролер (СК) служит для выработки

системных управляющих сигналов на основе слова состояния микропроцессора,

выдаваемого по шине данных. СК содержит (рис. 1.7):

· регистр, фиксирующий слово состояния

микропроцессора по сигналу  приходящему из ГСИ;

приходящему из ГСИ;

· шинный формирователь, формирующий

шину данных;

· логическую схему, вырабатывающую

сигнал подтверждения прерывания и сигналы управления памятью и внешними

устройствами.

Нагрузочная способность шин адреса и данных

микропроцессора ограничена в среднем одним ТТЛ входом или пятью выходами ТТЛШ.

Поэтому при реализации МПС необходимо выполнить расчет допустимой нагрузки

выходов микропроцессора. При превышении предельных значений требуется установка

шинных формирователей.

Рис. 1.7 Реализация системного контроллера

Для осуществления прерываний в МПМ могут

использоваться различные аппаратные средства, в частности в схеме, показанной

на рис.1.8. Первый триггер служит для предотвращения "дребезга"

контактов кнопки КН2, второй - для выдачи запроса на прерывание в

микропроцессор. После поступления от микропроцессора подтверждения запроса на

прерывание на шину данных микропроцессора подается код команды RST, соответствующей

реализуемому уровню прерывания.

Рис. 1.8 Реализация схемы обработки прерываний

Разработка модуля ввода-вывода

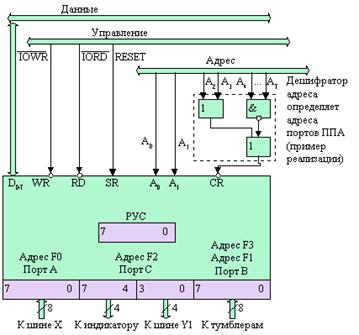

Для организации интерфейса с объектом и

организации обмена информацией с пультом управления в МПС использован ППА

КР580ВВ55. Интерфейс ППА и формат управляющего слова представлены на рис.1.9 и

рис.1.10.

Адресный дешифратор задает базовый адрес ППА, а

входы А0 и А1 ППА определяют номер его внутреннего регистра. Управляющее слово,

загруженное в регистр управляющего слова (РУС), настраивает порты ППА на

указанный режим и направление передачи.

Рис. 1.9 Интерфейс ППА

Рис. 1.10 Формат управляющего слова ППА

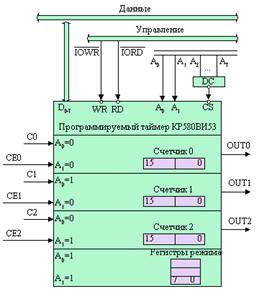

Модуль таймера предназначен для отсчета

временных интервалов при выработке сигналов y2 и y3. Модуль таймера реализован на

базе БИС программируемого таймера (ПТ) КР580ВИ53. Интерфейс кристалла ПТ и

формат его управляющего слова показаны соответственно на рис.1.11 и 1.12.

Рис. 1.11 Интерфейс программируемого таймера

ПТ содержит три 16-разрядных счетчика, каждый из

которых может работать в одном из шести режимов:

- программируемая задержка;

- программируемый одновибратор;

- программируемый делитель частоты;

- генератор меандра;

- строб с программным запуском;

- строб с аппаратным запуском.

Рис. 1.12 Формат управляющего слова

таймера

Подключение ПТ к системной магистрали аналогично

подключению ППА. Тактирование счетчиков ПТ может осуществляться от имеющегося в

МПМ генератора. Временные интервалы большой длительности могут быть обработаны

путем последовательного соединения двух счетчиков ПТ.

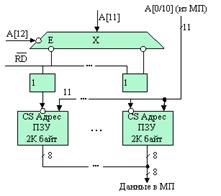

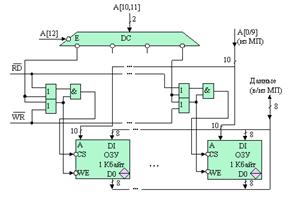

Разработка памяти МПС

Разработка памяти МПС должна начинаться с

определения ее емкости, требуемой для размещения программ (ПЗУ) и переменных

(ОЗУ). Разрядность памяти соответствует разрядности микропроцессора и равна

байту. Техническим заданием на курсовой проект определены конкретные типы ИС

ОЗУ и ПЗУ. Если для реализации необходимого объема памяти оказывается

недостаточно одной ИС ЗУ, потребуется модульная структура на основе нескольких

банков памяти, выбираемых адресным дешифратором (рис.1.13).

Сигналы управления памятью ( - выбор

кристалла и

- выбор

кристалла и  - разрешение

записи) формируются на основе системных управляющих сигналов, вырабатываемых

СК.

- разрешение

записи) формируются на основе системных управляющих сигналов, вырабатываемых

СК.

Рис 1.13 Пример организации

постоянной и оперативной памяти

Адресные дешифраторы построены так, чтобы

разделить физические адреса ячеек ПЗУ, ОЗУ и внешних устройств согласно

выбранной карте адресного пространства МПС. Микропроцессор по сигналу ”Сброс”

начинает выполнять программу с нулевого адреса, поэтому после ПЗУ должно иметь

начальные адреса. Из-за небольшого объема программ используется незначительная

часть адресного пространства МПС, поэтому может осуществляться неполная

дешифрация адресов, что сократит аппаратную сложность дешифраторов.

Итоговую структурную схему представим в

приложении 1.

. Краткое описание элементов схемы

Микропроцессор КР580ВМ80А - функционально

законченный однокристальный параллельный 8-разрядный микропроцессор с

фиксированной системой команд, применяется в качестве центрального процессора в

устройствах обработки данных и управления. Имеет 16-разряздый канал адреса, обеспечивающий

адресацию памяти объёмом до 64кбайт, адресацию 256 устройств ввода-вывода, а

также 8-разрядный канал данных.

Микропроцессор организован на работу с памятью,

имеющую байтовую организацию. Формат обрабатываемых данных имеет вид:

|

D7

(старший байт)

|

D6

|

D5

|

D4

|

D3

|

D2

|

D1

|

D0

(младший байт)

|

Микропроцессор КР580ВМ80А

реализован на основе общей внутренней магистрали данных и включает в себя

следующие функциональные узлы:

· блок

регистров с адресной логикой;

· блок

АЛУ;

· двунаправленную

буферизованную магистраль данных;

· блок

управления и синхронизации.

Условно графические обозначение микропроцессора

представлено на рисунке 2.1:

Рис. 2.1 Микропроцессор (МП)

КР580ВМ80

Шинный формирователь КР580 ВА86 -

двунаправленный 8-разрядный шинный формирователь, предназначен для обмена

данными между микропроцессором и системной шиной: обладает повышенной

нагрузочной способностью. Формирователь без инверсии с 3 состояниями на выходе.

КР580 ВА86 представляет собой

8-разрядный формирователь, обеспечивающий ток нагрузки 32 мА. Формирователь

имеет выход с 3 состояниями управляется сигналами направлениями передачи и

отключения. Условно графическое обозначение шинного формирователя представлено

на рисунке 2.2:

Рис. 2.2 Шинный формирователь

Адаптер связи КР580 ВВ55 - (ППА) микросхема

представляет собой программируемое устройство ввода-вывода параллельной

информации, применяется в качестве элемента ввода-вывода общего назначения,

сопрягающего различные типы периферийных устройств с магистралью данных систем

обработки информации. Схема позволяет осуществлять обмен 8-разрядными данными

по 3 каналам А, В, С. Направление обмена информации для каждого канала задаётся

программно. Режимы работы микросхемы задаются при её начальной установки путём

записи управляющего слова в регистр управления. Регистр С можно разделить на

два 4-разрядных регистра ввода-вывода данных, к которым осуществляется доступ

как к отдельным независимым регистрам.

Существует 3 режима работы каналов:

1. Режим 0-это простой ввод-вывод, при котором

возможны синхронная программно-управляющая передача данных через 4 независимых

управляемых порта,

2. Режим 1-позволяет осуществить обмен данными

через каналы А и С с помощью сигналов управления, передаваемых по каналу С.

3. Режим 2-канал А используется для

двунаправленной передачи данных, канал С для записи управляющих сигналов,

обеспечивающих передачи данных по каналу А.

Интегральный таймер КР580ВИ53- трех канальное

программируемое устройство (таймер), предназначенное для организации работы

микропроцессорной системы в режиме реального времени.

Эта микросхема представляет собой

программируемый 3 канальный таймер счётчик, вырабатывающий временные интервалы,

управляемые программой. Три канала программируются и работают независимо друг

от друга. Длительность интервалов может задаваться программно в 2-чной или 2-10

форме записи. Процесс формирования временных интервалов в каждом канале может

управляться внешним сигналом, подаваемым на вход разрешения работы. Работа

схемы тактируется до 2МГц.

Для каждого канала имеется возможность задания

одного из 6 режимов. микропроцессорный

управление оперативный постоянный

Режим 0-выдача сигнала прерывания по конечному

числу“1”. сохраняется до тех пор, пока в канал не будет перезагружен режим

работы или новое число: младший байт останавливает текущий счёт, старший байт

начинает новый счёт.

Режим 1-программирует ждущий мультивибратор.

Выход канала после загрузки числа в счётчик устанавливается в “0”, после

первого тактового сигнала. Одновременно начинается счёт, и при достижении

конечного числа на выходе устанавливается уровень “1”.

Режим 2-генератор тактовых сигналов. На выходе

канала через заданное число периодов тактовой частоты появляется “0”

длительностью в один период тактовой частоты. Число периодов определяется

числом, записанным в счётчик канала. Так как после установки режима работы

канала, сигнал на выходе “1” до окончания загрузки счётчика, то можно

осуществлять программную синхронизацию.

Режим 3-генератор прямоугольных сигналов. На

выходе канала будет высокий уровень в течении половины интервала времени и

низкий в течении другой половины.

Режим 4-программно управляемый строб. На выходе

канала появляется “1”, и когда на управляющий вход подается “1”, начинается

счет и при достижении конечного числа на выходе устанавливается “0”

длительностью в один период тактовой частоты.

Режим 5-строб с аппаратным запуском. Счетчик

канала после загрузки начинает счет только по переднему фронту на управляющем

входе. Если, во время счета на управляющем входе появится передний фронт

сигнала, то счет будет начат сначала. Установка режима работы каналов

осуществляется путем записи управляющего слова в регистр режим канала.

Рис. 2.4 Программируемый таймер

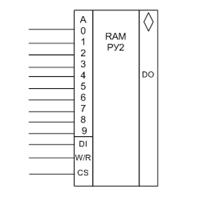

Оперативное запоминающее устройство К155РУ2

Микросхемы могут работать в режимах записи,

считывания и хранения информации. У микросхемы К155РУ2 доступ к накопителю (в

режиме записи или считывания) возможен только при соответствующих комбинациях

сигналов CS: CS1=0,

CS2=0,

CS3=1.

Рис. 2.5 ПЗУ Рис. 2.6

ОЗУ

ОЗУ предназначено для кратковременного хранения

текущей информации, относящейся к решаемой задаче. В ОЗУ статического типа в

качестве запоминающего элемента используются триггеры. Режим работы микросхемы

задается сигналами, поступающими на управляющие входа со схемы управления.

Условно графическое обозначение микросхемы

приведено на рисунке 2.5:

Постоянное запоминающее устройство К155РЕ3

ПЗУ предназначено для постоянного хранения

программы. Чтение информации из микросхемы задается сигналами, поступающими на

управляющие входы со схему управления.

3. Описание электрической

принципиальной схемы

При включении микропроцессорной системы,

происходит начальная установка микропроцессора, в течение 3-4 тактов. После

чего начинает выполняться моделирующая программа. Во время выполнения

программы, процессор можно сбросить в исходное состояние, путем включения

кнопочного переключателя S1(КН1). Выполнение программы можно прервать с помощью

кнопочного переключателя S2(КН2), после его нажатия происходит выполнение

прерывающей программы. Обмен информации производят, как дано по заданию, по

общей шине.

Для синхронизации работы узлов используется

генератор тактовых импульсов. Генератор формирует сигналы С1 и С2 с частотой

2МГц.

Для управления работой МПС вырабатывает

управляющие сигналы: RD,

WR, IORD,

IORW.

Для ввода-вывода информации используется

параллельно-периферийный адаптер (ППА) КР580ВВ55.

Программирование режима работы ППА производится

следующим образом:

-управляющее слово.

Для настройки ППА следует записать команду:A,

92h- управляющее слово в накопитель.83h-запись в РУС.

Для выбора одного из каналов используются входы

А0, А1 и выбор устройства (CS)-8

разрядом адреса через инвертор.

Порт А-80h, порт В-81h, порт С-82h, РУС-83h.

Для обращения к ППА как к ВУ подключаются входы

WR, RD к IORD и IORW шины управления.

Для организации временных интервалов при работе

МПС используется интервальный таймер КР580ВИ53. Процесс формирования временных

интервалов в каждом канале будет инициализироваться внешними сигналами,

подаваемые на вход разрешения работы.

Работа схемы тактируется сигналами внешнего

генератора с частотой 2МГц. Входы А0, А1, используются для активизации одного

из каналов или регистра управления, а выбор самого интервального таймера 8

разрядом адреса: СЧ0-00h, СЧ1-01h, СЧ2-02h, РУС-03h.

Режим работы микросхемы КР580ВИ53 задаются при

начальной установке. Каналы схемы полностью не зависят друг от друга, и каждый

может иметь свой режим работы. Интервальный таймер программируется таким

образом, что СЧ0 работает как делитель входной частоты. Это необходимо для

того, чтобы получить миллисекундный диапазон для выдачи У3. СЧ1 работает в

режиме 0, т.е. в режиме программируемой задержки, время задержки равно У3,

время задержки можно увеличить кнопкой КН3. СЧ2 работает в режиме 3, т.е. как

генератор прямоугольных импульсов, длительность периода равна У2.

4. Блок схема алгоритма и программа

Алгоритм - конечная последовательность точно

определенных действий, приводящих к решению поставленной задачи. Причем

алгоритм работы программы будет представлен на рисунке 4.1.

Рис. 4.1 Алгоритм работы программ

Причем в программе предусмотрен вызов функции по

прерыванию. Алгоритм функции прерывания представим на рисунке 4.2.

Рис. 4.2 Алгоритм работы функции вызываемой по

прерыванию

Так как в эмуляторе процессора не было

возможности провести настройку таймера, я осуществил вывод в порт значения

подсчитанного периода Y2.

Программа на языке ассемблер является пошаговой

логической реализацией алгоритма. При написании программы разработчик должен

использовать адреса только реально имеющихся ячеек.

После начальной установки начинается выполнение

программы по заданному алгоритму. Вначале в указатель стека загружается адрес

вершины стека, затем происходит переход на основную программу. Программируется

ППА и вводятся значения Х и К, после чего разрешаются прерывания. Затем

производятся вычисления значения У3, осуществляется программирование СЧ0 и СЧ1

интервального таймера и в СЧ1 загружается У3. После этого выполняется

прерывание RST5 (для этого в эмуляторе процессора надо запустить программу на

выполнение F6 и прерывание

вызывать по F7, а дальне ввести

номер прерывания), это прерывание вычисляет значение У2, который заносится в

СЧ2 интервального таймера. После возвращения в основную программу, происходит

вычисление У1 и У светодиодной индикации. Полученный байт выводится через порт C.

После вывода байта происходит прием операндов: Х через порт А, К через порт В,

программа возвращается на вычисление У1 и У. У2 вычисляется с новыми значениями

Х и К, только после принудительного прерывания. У3 вычисляется один раз.

Листинг программы с пояснениями приведен в

приложении 2.

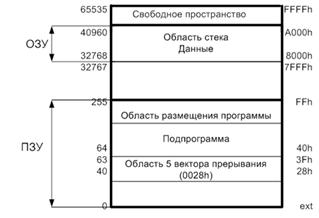

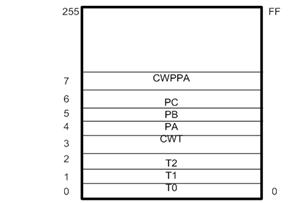

5. Карта распределения адресного

пространства памяти

Память - один из основных элементов устройства.

Она организована как множество ячеек, в которых может храниться информация.

Совокупность всех ячеек памяти, к которым может обратиться МП, составляет

адресное пространство памяти. Информационная емкость одной ячейки составляет 8

бит или 1 байт.

Наибольший объем памяти, который может быть

использован в устройстве, определяется объемом адресного пространства.

Важным этапом конструирования ЭВМ является

организация памяти, и поэтому при разработке программного обеспечения важно

внимательно провести распределение памяти. ПЗУ находится в области памяти с

0000 по FFh. ОЗУ

находится в области с 8000h

по A000h.

Рис. 5.1 Карта распределения адресного

пространства памяти

Рис. 5.2 Карта распределения УВВ

Адреса 0-255 отведенены под ПЗУ. По адресу 0h

в ПЗУ размещена 1 команда JMP

START. Диапозон по

адресу 40 записана команда вызова подпрограммы PRER.

Диапазон УВВ - адреса 0-3 используются для

адресации устройств ПИТ, 4-7 для адресации трех портов ППА - PA,

PB,PC

и регистра слова управления ППА

6. Оценка ёмкости ПЗУ и ОЗУ

Команды и данные необходимо хранить и выбирать

по мере необходимости в процессе работы ЭВМ. Для этой цели применяют ЗУ. Их

можно разделить на два типа: ОЗУ и ПЗУ. ПЗУ используется для хранения команд и

констант. Запись в ПЗУ сложна и занимает много времени, поэтому этот тип памяти

применяется в тех случаях, когда не требуется изменять записанную однажды

информацию. В данном курсовом проекте выбрана из задания ПЗУ К155РЕ3 (32*8), а

так как программа, реализующая алгоритм работы МПС занимает всего 198 байт (С6h),

то нам достаточно 7микросхем, для лучшей совместимости и облегчения

программирования возьмем 8 микросхем.

ОЗУ используется для хранения данных,

изменяющихся в процессе работы системы. Блок ОЗУ построен на основе 8 микросхем

КР155РУ2 (1к*1).

7. Расчет потребления тока

Таблица

7.1

Потребление тока

|

Тип

м/c

|

Колич-во

(шт)

|

Iпотр+5В (мА)

|

Iпотр+12В (мА)

|

Iпотр-5В (мА)

|

|

КР580ВМ80А

|

1

|

70

|

50

|

1

|

|

КР580ВК28

|

1

|

190

|

|

|

|

КР580ВИ53

|

1

|

140

|

|

|

|

КР580ВВ55

|

1

|

120

|

2

|

160

|

|

|

|

КР580ИР82

|

1

|

250

|

|

|

|

К580ГФ24

|

1

|

123

|

12

|

|

|

К155РУ2

|

8

|

140

|

|

|

|

К155РЕ3

|

8

|

138

|

|

|

Таким образом по данным таблицы ток потребления Iпотр.

cоставляет:

· от источника +5В: 2609 мА.

· от источника +12В: 72 мА.

· от источника -5В: 1 мА.

ЗАКЛЮЧЕНИЕ

В процессе выполнения курсового проекта, была

спроектирована схема микропроцессорной системы управления некоторым объектом. В

пояснительной записке представлен подробный синтез структурной и принципиальной

схемы.

Составлен алгоритм работы МПС, разработана

программа обеспечивающая выполнение заданного алгоритма, также была

распределена область памяти под ОЗУ и ПЗУ. Проведена организация оперативной и

постоянной памяти.

Был произведен расчет потребления тока от

источника питания. Был оформлен чертеж микропроцессорной системы в виде

структурной и принципиальной схемы.

Данный проект может быть использован для

создания микроконтроллера автоматизированного управления удаленным объектом.

СПИСОК ЛИТЕРАТУРЫ

1. Лебедев

О.Н. Применение микросхем памяти в электронных устройствах: Справ. Пособие.-

М.: Радио и связь,1994.-216с.

2. Справочник

Большие интегральные схемы ЗУ/ под редакцией Гордонова А.Ю., Дьяконова Ю.Н.

. Справочник

Полупроводниковые БИС ЗУ / под редакцией Гордонова А.Ю., Дьяконова Ю.Н.

. Учебный

микропроцессорный комплект: Техническое описание и руководство оператора.

. Каган

Б.М. Электронные вычислительные машины и системы: Учеб. пособие для вузов.- 3-е

изд., перераб. и доп.- М.: Энергоатомиздат1991.- 592 с.

. Шевкопляс

Б.В. Микропроцессорные структуры. Инженерные решения: Справочник.- 2-е изд.

перераб. и доп.- М.: Радио и связь, 1990.- 512 с.

ПРИЛОЖЕНИЕ 1

Структурная схема МПС

ПРИЛОЖЕНИЕ 2

Листинг программы:

Ассемблер K580.Файл: kurs.as

T0 EQU

0

T1 EQU 1EQU 2EQU 3EQU 4EQU 5EQU 6EQU

7EQU 409600START40PRER: LXI

SP,STEAK

MVI

A, 10010010B;

Установка ППА в режим ввода по OUT

CWPPA;

PA и PB

и вывода по PC

call vvodXKy3:y1ledvvodXKbegin:

a,01010000b;установка

T1 ПИТ - реж. 0

out CWTa,c ;вычисление

y3=2*max(x,k)bm1endy3: mov a,b3:add

a

out

T1 ;запись в регистр

T1 зачения интервала

времени Y3=0a,00111110b; установка Т0 в - реж.

3CWTa,11101000b; запись в регистр Т0 числa

out

T0 ; коэффициент

деление

mvi a,00000011b ;равногоT0

; 1000: in PPA ;ввод Х

b,a;

В рег. В сохраняем значение Х

in

PPB;ввод К

mov

c,a;

В рег. С сохраняем значение А

ret

y1:mov

a,c

add abm2endy1: mov a,b:add b

0fh ;выделение младшей

тетрады

out

PPC ;вывод в порт С

ret

:mov a,ccccd,aa,cb10hendl: mvi a,10h:sub

d

ani 11110000b

;выделение старшей тетрадыPPC ;вывод в порт С

ret:pswbdha,bcd,aa,cbm4endr: mov

a,b:add dd,aA,10111110b; ПИТ

- реж.

3CWTa,dT2

hdbpsw