Разработка вычислительного устройства для выполнения операции умножения двоичных чисел

ОГЛАВЛЕНИЕ

РЕФЕРАТ

ВВЕДЕНИЕ

1.

Арифметическо-логические устройства ЭВМ

.1

Назначение, состав и структура АЛУ

.2

Классификация АЛУ

.3

Средства представления АЛУ

.

Словесное описание операции умножения

.

Синтез АЛУ

.

Блок-схема алгоритма выполнения операции

.

Определение набора управляющих сигналов

.

Структурная схема устройства

.

Временная диаграмма управляющих сигналов

.

Схемное решение устройства управления

.

Микропрограмма выполнения команды умножения

ЗАКЛЮЧЕНИЕ

СПИСОК

ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ

РЕФЕРАТ

Курсовой проект Ладыженко Е.А.

Тема: Разработка вычислительного устройства для

выполнения операции умножения двоичных чисел»

Объем работы 27 с., в том числе 3 табл., 3 наим.

лит., 4 чертежа, 1 рисунок.

Целью курсового проекта является изучение

принципов построения и функционирования АЛУ для умножения на один разряд

множителя чисел с фиксированной точкой со знаком, заданных в прямом коде,

начиная с младших разрядов множителя, со сдвигом частного произведения влево.

В курсовом проекте решаются следующие задачи:

· рассматривается словесное описание

операции умножения;

· строиться блок-схема алгоритма

умножения и определяется набор управляющих сигналов;

· определяется набор составляющих АЛУ

элементов;

· определяются связи между элементами

и порядок функционирования устройства;

· строиться временная диаграмма

управляющих сигналов;

· разрабатывается микропрограмма

выполнения команды умножения.

ВВЕДЕНИЕ

Цель этого проекта заключается в разработке

вычислительного устройства для выполнения операции умножения двоичных чисел, с

фиксированной точкой со знаком, представленные в прямом коде. Исходными данными

являются количество разрядов (коды чисел): Мн=4 (0.0101); Мт=6(0.101010), и

алгоритм умножения: на один разряд множителя, начинается с младших разрядов

множителя, со сдвигом частного произведения влево.

При создании этого проекта предполагается

словесно описать операции умножения, определит набор управляющих сигналов,

синтезировать АЛУ (Арифметика-логическое устройство), выделить схемное решение

и наконец написание микропрограмму выполнения команды умножения.

Проектирование АЛУ включает выбор кодов для

представления данных, определение алгоритмов выполнения отдельных операций,

структур операционных блоков и реализуемых в них наборов микроопераций. Затем

производят объединение отдельных операционных блоков и соответствующих наборов

микроопераций в один многофункциональный операционный блок или несколько блоков

для отдельных групп операций. Стремление обеспечить возможность эффективного

объединения операционных блоков отдельных операций влияет на выбор их структур.

Одним из способов решения проблемы с

фиксированной точкой можно решить следующим способом: так как в ЭВМ операции

умножения чисел с фиксированной точкой с помощью соответствующих алгоритмов

сводиться к операциям сложения и сдвига.

При умножении двух чисел произведение

формируется суммированием частичных произведений. В зависимости от цифры

множителя к сумме частичных произведений прибавляется либо множимое, либо ноль.

Произведение двух n-разрядных чисел с фиксированной

запятой, в нашем случае может иметь 2 значащих разрядов.

Поэтому необходимо предусмотреть возможность

формирования в АЛУ произведения, имеющего двойную длину по сравнению с

исходными числами.

1. АРИФМЕТИКО-ЛОГИЧЕСКИЕ УСТРОЙСТВА ЭВМ

.1 Назначение, состав и структура АЛУ

Все основные операции по преобразованию данных в

ЭВМ производятся в операционных блоках, которые в большинстве случаев

называются арифметическо-логическим устройством. Набор операций, выполняемых

АЛУ универсальных ЭВМ, должен быть функционально полным, т.е., обеспечивать

реализацию любого вычислительного алгоритма. И хотя функциональную полноту

можно обеспечить очень узким набором операций, число различных операций,

выполняемых в АЛУ, обычно составляет от нескольких десятков до нескольких

сотен. Это обеспечивает сокращение длины программ и повышение быстродействия

ЭВМ в целом.

Как правило, в любом АЛУ предусмотрена

возможность выполнения четырех основных арифметических операций, нескольких

логических операций, а также сдвигов. Набор операций АЛУ является одной из

основных его характеристик.

Так как АЛУ является законченным в

функциональном отношении устройством, то на него распространяются общие

закономерности технических систем. Поэтому в составе АЛУ в общем случае можно

выделить четыре группы узлов, соответствующих основным системным процессам:

хранения, передачи, преобразования, управления.

К узлам хранения в АЛУ относятся:

· регистры, обеспечивающие хранение

операндов, промежуточных и окончательных результатов;

· триггеры, позволяющие хранить

различные признаки результатов или какие либо вспомогательные биты.

В некоторых случаях регистры АЛУ образуют блок

регистровой памяти, а триггеры (называемые также флажками) объединяются в

регистр состояния.

К узлам передачи, имеющимся в АЛУ, относятся:

· шины, соединяющие отдельные блоки

АЛУ;

· блоки вентилей (схем И)

· мультиплексоры, обеспечивающие

выполнение передачи по выбранному направлению и в нужный момент времени.

К группе узлов преобразования могут относиться:

· сумматоры, выполняющие в ряде

случаев несколько различных микроопераций;

· схемы выполнения логических

операций, иногда совмещаемые с сумматорами;

· схемы коррекции, например, для

операций десятичной арифметики;

· схемы сдвига (сдвигатели);

· преобразователи кодов, служащие для

получения обратных или дополнительных кодов;

· счетчики, используемые для

вспомогательных преобразований;

· для подсчета числа циклов в

циклических операциях.

К узлам управления можно отнести:

· блок управления АЛУ (если таковой

имеется отдельно);

· дешифраторы управляющих сигналов

(кодов);

· схемы формирования логических

условий (признаков);

· для организации ветвлений в

микропрограммах выполнения операций.

Конечно, следует учитывать, что любое

разделение, классификация имеют элемент условности и можно найти достаточно

примеров, когда один узел можно отнести к различным группам, В частности, в

рассматриваемом случае мультиплексоры и блоки вентилей можно отнести как к

узлам передачи, так и к узлам управления, так как они разрешают или запрещают

передачу.

Арифметическо-логическое устройство включает

узлы перечисленных групп, соединенные тем или иным способом в некоторую

структуру. Структурные схемы АЛУ могут быть различными, что определяется

различием принципов их построения.

Помимо набора операций и структурной

организации, АЛУ характеризуются еще рядом показателей. К ним относятся

разрядность обрабатываемых чисел (кодов), времена выполнения различных операций

или, иногда, усредненное быстродействие, наличие дополнительных функциональных

возможностей типа контроля правильности выполнения операций, устойчивости к

отказам, а также конструктивные характеристики, такие как габариты,

энергопотребление, надежность и пр.

1.2 Классификация АЛУ

В процессорах современных ЭВМ используются

различные по своей организации АЛУ. Эти различия обусловлены функциональным

назначением АЛУ, способами реализации операций, требованиями по быстродействию

и др. Основные характерные особенности того или иного АЛУ можно отнести к одной

из трех групп: особенности обрабатываемой информации, организации выполнения

операций и структурной организации. Рассмотрим эти группы несколько подробнее.

Обрабатываемая в АЛУ информация представляет собой либо численные, либо

логические величины (и те и другие могут иметь различную организацию). Как

известно, численные величины в ЭВМ представляются по-разному. Это проявляется,

в основном, в используемых формах представления данных, системах счисления,

разрядности, применяемых кодах. По этим признакам АЛУ можно разделить следующим

образом. По форме представления чисел: АЛУ с фиксированной запятой; АЛУ с

плавающей запятой; АЛУ с фиксированной и плавающей запятыми (универсальные).

Причем в рамках каждого представления имеются некоторые различия, влекущие за

собой особенности процедур выполнения операций либо структуры АЛУ. Так, числа с

фиксированной запятой могут быть представлены в виде целых или в виде дробных

чисел, меньших единицы. Это сказывается на особенностях выполнения операций

умножения и деления. Числа с плавающей запятой могут иметь мантиссу и порядок

(целое со знаком) или мантиссу и характеристику (смещенный порядок), что влияет

на процедуры обработки порядков.

Кроме того, следует также упомянуть наличие и

других форм представления, используемых в калькуляторах: так называемая

автоматическая запятая, при которой положение запятой в результате операции

определяется количеством разрядов дробной части чисел, участвующих в операции;

естественная запятая - то же для целых частей.

По используемой системе счисления: АЛУ,

работающие в позиционной системе счисления; АЛУ, работающие в непозиционной

системе счисления.

Известны также случаи использования троичной

системы счисления, некоторые работы с R-значными системами, разработки по

использованию систем счисления, веса двоичных разрядов в которых соответствуют

числам Фибоначчи.

Из непозиционных систем счисления в арифметике

используется система остаточных классов (СОК), числа в которой представляются в

виде остатков от деления исходного числа на набор взаимно простых чисел,

называемых основаниями системы. Такое представление обеспечивает возможность

независимой обработки разрядов (остатков) чисел, что, в частности, представляет

интерес для цифровой оптической обработки информации. По разрядности

обрабатываемых чисел: АЛУ, выполняющие операции над числами (кодами)

фиксированной разрядности; АЛУ, обрабатывающие операнды переменной длины. В

обоих случаях само АЛУ имеет фиксированную разрядность блоков, но во второй

группе предусмотрены специальные средства, обеспечивающие обработку операндов

по частям, и соответствующие микропрограммы выполнения операций. Имеются также

АЛУ, в которых операции выполняются над несколькими различными видами операндов

фиксированной разрядности, обычно это форматы полуслова, слова и слова двойной

длины.

По кодам, используемым для представления

отрицательных чисел: АЛУ с использованием обратных кодов; АЛУ с использованием

дополни тельных кодов. Принципиальных особенностей структур АЛУ это различие не

обусловливает. Известны и устройства, в которых одни операции выполняются с

использованием обратных кодов, а другие - дополнительных. Особенности

структурной организации АЛУ определяются составом операционных блоков

устройства и характером связей между ними. В этой группе признаков АЛУ можно

подразделить следующим образом.

По количеству операционных блоков: одноблочные

АЛУ (иначе, универсальные или многофункциональные) и многоблочные АЛУ. В первых

из них имеется операционный блок, в котором может выполняться любая из операций

АЛУ. Такая организация характерна для ЭВМ невысокой производительности.

Многоблочные АЛУ имеют в своем составе несколько операционных блоков, каждый из

которых ориентирован на выполнение какой-либо одной операции, например

умножения, или нескольких операций, например сложения и логики. Причем

предусматривается одновременная работа различных блоков, что, совместно со

специализацией блоков, обеспечивает более высокую производительность ЭВМ с

такими АЛУ.

По характеру связей: устройства с магистральными

и с непосредственными связями. Для первых из них характерно наличие внутренней

шины данных, по которой осуществляются все передачи информации между любыми

узлами АЛУ. В случае непосредственных связей в структуре предусматривается

набор индивидуальных шин, связывающих пары узлов, между которыми должны

выполняться передачи.

Структурные особенности определяются также и

назначением ЭВМ, в состав которых входит АЛУ, в целом. Так, например, в

специализированных системах для обработки сигналов операционные блоки могут

иметь структуру, наиболее приспособленную к алгоритмам обработки.

Особенности организации выполнения операций

(процесса обработки) проявляются в принципах получения результатов и порядке

обработки данных. По этим признакам возможны следующие подразделения. По

принципу получения результата: АЛУ с алгоритмической реализацией операций;

табличные АЛУ; таблично-алгоритмические АЛУ. АЛУ с алгоритмической реализацией

операций - наиболее распространенный тип. В них каждая операция (кроме самых

простых) представляется в виде последовательности более простых преобразований

- микроопераций. Последовательность этих преобразований определяется алгоритмом

выполнения операций. Реализуется такая последовательность либо за несколько

тактов под управлением соответствующей микропрограммы, обеспечивающей

необходимую настройку узлов АЛУ в каждом такте, либо за один такт, при наличии

для всех микроопераций отдельных узлов, соединенных в требуемой

последовательности. В табличных АЛУ результат операции не вычисляется каждый

раз при ее выполнении. Он выбирается из таблицы - постоянной памяти, в которой

заранее записаны назначения результатов, соответствующие всем возможным

значениям операндов. Такой способ наиболее эффективен для вычисления сложных функций

одного аргумента при небольшой его разрядности, например, тригонометрических

функций. Применим он и для реализации обычных арифметических операций. При

выполнении операций в табличных АЛУ значение аргумента (аргументов) используют

в качестве адреса ячейки ПЗУ, в которой записан результат, соответствующий

этому значению (значениям). Табличный способ обеспечивает высокую скорость

обработки, так как независимо от сложности реализуемых преобразований все

действия сводятся к считыванию готового результата из ПЗУ. Однако недостатком

его является необходимость очень большого объема памяти (таблицы) при

увеличении разрядности операндов.

Таблично-алгоритмические АЛУ представляют собой

компромисс между первыми двумя способами. В них результат получается сочетанием

этих способов. Часть разрядов операндов (обычно старшие разряды) используется

для получения приближенного значения результата табличным способом. По

остальным разрядам вычисляется поправка к предварительному результату.

Этот метод позволяет сократить объем таблиц при

сохранении относительно высокой скорости и находит применение в мощных ЭВМ.

По порядку обработки данных: последовательные

АЛУ, параллельные

АЛУ и конвейерные АЛУ. Эти АЛУ различаются между

собой по степени параллелизма в выполнении операций. Так, в АЛУ

последовательного типа обработка операндов осуществляется последовательно

разряд за разрядом. В АЛУ параллельного типа операции производятся одновременно

над всеми разрядами операндов.

Известны также промежуточные варианты

организации АЛУ - параллельно-последовательные, в которых обработка операндов

осуществляется одновременно по группам разрядов, тогда как группы

обрабатываются между собой последовательно. В АЛУ конвейерного типа параллелизм

имеет место на уровне операций, т.е. в них возможно выполнение нескольких

операций одновременно. Термин «конвейерные АЛУ» имеет различные интерпретации.

В ряде случаев его применяют к многоблочным АЛУ. Например, АЛУ, имеющее в

качестве отдельных блоков сумматор, устройство умножения и устройство деления может

обеспечивать конвейерную обработку. С другой стороны, сами устройства умножения

и деления могут быть конвейерного типа и реализовать сразу несколько операций

умножения или деления, которые в один и тот же момент времени пребывают в

разных стадиях своего выполнения. Эти варианты конвейеров называют конвейерами

последовательного типа в отличие от векторных конвейеров, выполняющих операции

над векторами.

Очевидно, что чем выше степень параллелизма,

заложенного в структуре АЛУ, тем более высокопроизводительным оно является.

Однако сложность схем, а следовательно, аппаратные затраты на реализацию таких

АЛУ и управление ими тоже возрастают. Следует отметить, что возможны также

подразделения АЛУ и по некоторым другим признакам.

.3 Средства представления АЛУ

Необходимость в представлении АЛУ возникает в

различных случаях:

а) при описании устройств в литературе,

документации, рекламе;

б) при их проектировании, как ручном, так и

автоматизированном;

в) при моделировании функционирования с целью

анализа характеристик и проверки правильности работы.

При этом, поскольку ЭВМ в целом и АЛУ можно

отнести к классу многоуровневых систем, их представление может осуществляться

на различных уровнях детализации: начиная от уровня электронных компонентов

логических элементов и кончая уровнем всего устройства в целом. Кроме того,

представление АЛУ (ЭВМ) может быть ориентировано на описание структуры

устройства, его функционирования и его технической реализации. Поэтому для

различных целей и уровней представления АЛУ должны существовать различные

средства, формальные и языковые. (Помимо этого, несколько самостоятельной, но

тесно связанной с ними областью являются описания процессов проектирования

цифровых устройств.)

Начало систематической разработки средств

представления ЗВМ принято относить к 60-м годам XX столетия, когда стали

появляться языки для описания аппаратных средств ЭВМ. Нетрудно заметить, что

появление этих языков последовало за разработкой языков программирования. Но

понятно, что средства представления ЗВМ существовали и на более ранних периодах

развития вычислительной техники. Они заимствовались как из математических, так

и из инженерных (электротехнических, радиотехнических, связных) дисциплин. Из

математических дисциплин были заимствованы аппарат булевых функций и алгоритмические

представления процессов вычислений. Из инженерных дисциплин были использованы

представления в виде электрических схем, блок-схем. На первых порах, когда

вычислительные машины были относительно просты, а проектирование их велось

исключительно вручную, таких представлений было достаточно. Однако с

усложнением самих ЭВМ, увеличением числа уровней иерархии в них, развитием

методов их проектирования и теоретических разработок понадобились более

пригодные для машинного использования формализованные методы описания ЭВМ. В

результате были созданы различные формальные модели и языковые средства,

ориентированные на различные уровни представления и целевое назначение. В

большинстве случаев эти средства не были узкоспециализированными и значительная

часть из них пригодна для использования на различных уровнях и для разных

целей. При представлении ЭВМ и систем в зависимости от степени детализации

различают от четырех до семи и более уровней. Один из возможных вариантов,

включающий шесть уровней представления структуры и соответствующие им процессы

функционирования и техническую реализацию, а так же средства представления,

приведен в таблице (см. таблицу 1.1)

арифметический логический

управляющий сигнал

Таблица

1.1

Уровни и средства представления вычислительных

устройств

|

Уровень

представления структуры

|

Процессы

функционирования

|

Техническая

реализация

|

Средства

представления: структуры функционирования реализации

|

|

1.

Электронные схемы

|

Токи

в эл. цепях

|

Радио-компоненты

|

Электрическая

схема (принципиальная)

|

Диф.

уравнения для токов и напряжений

|

Фотошаблоны

масок интегральных схем

|

|

2.

Логические схемы

|

Логические

преобразования, Переключение состояний элементов памяти

|

Интегральные

схемы

|

Схема

из логических элементов (электрическая принципиальная)

|

Булевы

функции булевы автоматы

|

Топология

интегральных схем (языки графические)

|

|

3.

Узлы и блоки

|

Выполнение

микроопераций

|

Интегральные

схемы, конструктивы (плата, ТЭЗ), их фрагменты

|

Схемы

из логических элементов и узлов (Электрическая функциональная)

|

Языки

регистровых передач (микроопераций)

|

Планы

кристалла (языки графического типа)

|

|

4.

Устройства

|

Выполнение

микропрограмм

|

Интегральные

схемы, платы, ТЭЗы, панели, стойки

|

Схемы

из узлов и блоков (электрические, структурные)

|

Языки

регистровых передач, языки описания микропрограмм

|

Укрупненный

план кристалла, чертежи конструктива

|

|

5.

ЭВМ

|

Выполнение

программ (команд)

|

Конструктивы

всех уровней.

|

Структурные

схемы

|

Языки

команд, языки программирования

|

Чертежи

конструктива

|

|

6.

Системы

|

Взаимодействие

устройств, вычислительный процесс

|

Конструктивы

всех уровней.

|

Структурные

схемы

|

Языки

моделирования систем, сетевые модели

|

Чертежи

конструктивов

|

2. СЛОВЕСНОЕ ОПИСАНИЕ ОПЕРАЦИИ УМНОЖЕНИЯ

В ЭВМ операции умножения чисел с фиксированной

запятой с помощью соответствующих алгоритмов сводиться к операциям сложения и

сдвига. При умножении двух чисел произведение формируется суммированием

частичных произведений. В зависимости от цифры множителя к сумме частичных

произведений прибавляется либо множимое, либо ноль. Произведение двух

n-разрядных чисел с фиксированной запятой может иметь значащих разрядов.

Поэтому необходимо предусмотреть возможность формирования в АЛУ произведения,

имеющего двойную длину по сравнению с исходными числами.

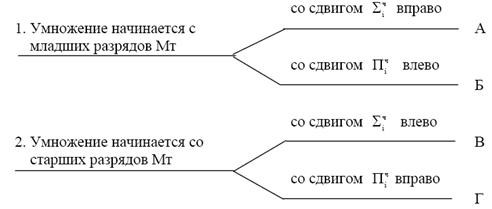

В зависимости от способа

формирования суммы частичных произведений различают четыре метода выполнения

умножения (рисунок 2.1). Введем некоторые обозначения, используемые ниже: пч - частичное произведение,

- частичное произведение,

- частичная сумма, Mн -

число-множимое, Мт - число-множитель.

- частичная сумма, Mн -

число-множимое, Мт - число-множитель.

Рисунок 2.1 - Схема алгоритмов

умножения

Так как в нашем случае походит (алгоритм Б),

представим, что

Мн = А = 0,

…

…

Тогда (алгоритм Б) имеет вид:

Мн·Мт = С=А·В = 0+ b1·A+

b2A2+…+

Умножение, начиная с младших разрядов множителя,

при сдвиге множимого влево и неподвижной сумме частичных произведений, регистр

множимого и сумматор частичных произведений имеют двойную длину. Регистр

множителя при этом должен иметь цепи сдвига вправо, регистр множимого цепи

сдвига влево, а сумматор частичных произведений не содержит цепей сдвига.

Последовательность действий определяется, как и в первом варианте, младшим

разрядом регистра множителя. При этом методе регистр множимого и сумматор

частичных произведений должны иметь двойную длину. Этот метод требует больше

оборудования, но никаких преимуществ не дает.

3. СИНТЕЗ АЛУ

Синтез АЛУ проходит в несколько этапов:

. Сначала необходимо выбрать метод, по которому

предполагается выполнение операции.

. Составить словесный алгоритм соответствующих

действий.

. Построить блок-схему алгоритма и определить

набор управляющих сигналов.

. Исходя из алгоритма и формата исходных данных,

следует определить набор составляющих АЛУ элементов.

. Затем требуется определить связи между

элементами и установить порядок функционирования устройства.

. Построить временную диаграмму управляющих

сигналов, которые должны быть поданы на АЛУ от устройства управления.

Представим расчёты числа с фиксированной точкой

со знаком, представленные в прямом коде; алгоритм умножения на 1 разряд

множителя, начиная с младших разрядов множителя со сдвигом частного

произведения влево. Рассмотрим алгоритм решения задачи. Имеются два числа:

Мн = 0.0101;

Мт = 0.101010,

где y0

=

1, y1 =

0, y2 =

1, y3 =

0, y4 = 1, y5=0.

Вычисления выполняются по формуле:

Мн·Мт = С=А·В = 0+·A+ A2+…+

A2+…+

Вычисления:

Z = 0 - начальное

содержимое сумматора;

y1 = 1 + 1010 0•X•2-1

- первое частичное произведение;

00000000 Z

= Z + X•2-1

- первая частичная сумма;

y2 = 0 + 1010 1*X

•2-2 - второе частичное произведение;

Z = Z

+ 0 - вторая частичная сумма;

y3 = 1 + 1010 0•X•2-3

- третье частичное произведение;

10101000 Z

= Z + X•2-3

- третья частичная сумма;

y4 = 0 + 0000 1•X•2-4

- четвёртое частичное произведение;

Z

= Z + X•2-4

- четвёртая частичная сумма;

y5= 1 + 10100 0•X•2-5

- пятое частичное произведение;

01100100 Z

= Z + X•2-5

- пятая частичная сумма;

y6= 0 + 1010 1•X•2-6

- шестое частичное произведение;

Z = Z

+ X•2-6 -

результат умножения.

Проверка: 0.0101 = 5; 0.101010 = 42; 5*42=210;

210 = 11010010

После рассмотрения словесного алгоритма операции

умножения необходимо построить блок-схему алгоритма и определить набор

управляющих сигналов.

4. Блок-схема алгоритма

выполнения операции

Блок-схема алгоритма умножения на один разряд

чисел с фиксированной точкой со знаком, заданных в прямом коде, с младших

разрядов множителя, со сдвигом частного произведения влево представлена на

чертеже 01.24.006.01.

Блок 1: загрузка регистра множителя RGX;

Блок 2: загрузка регистра множимого RGY;

Блок 3: установка сумматора в «0»;

Блок 4: загрузка знака множителя в триггер TX;

Блок 5: загрузка знака множимого в триггерTY;

Блок 6: определение знака произведения TZ=TX+TY;

Блок 7: производит сдвиг частной суммы влево на

один разряд X=X*21;

Блок 8: проверяет значения разрядов множителя yi=0;

Блок 9: присваивает к сумме частичных

произведений множимое Z=Z+X;

Блок 10: присваивает к сумме частичных

произведений Z=Z+0;

Блок 11: производит сдвиг частной суммы на один

разряд X=X*21;

Блок 12: счётчик циклов i=i+1;

Блок 13: проверка условия i>n.

5. Определение набора

управляющих сигналов

Каждой переменной, представленной в алгоритме, в

схеме должен соответствовать элемент хранения. Разрядность модуля произведения

равна сумме разрядностей сомножителей. Умножение двоичного числа на 2i

обеспечивается

сдвигом этого числа влево на соответствующее количество разрядов. Переход к

анализу очередного разряда множителя (i=i+1) может быть обеспечен сдвигом

регистра множителя на один разряд в сторону старших разрядов.

Исходя из этого, определим состав оборудования,

необходимого для реализации АЛУ заданного типа для n = 10 (таблица 4.1).

Таблица

4.1

Состав оборудования, необходимого для реализации

АЛУ

|

Схема

|

Разрядность

|

Функции

|

Управляющий

сигнал

|

|

Регистр

модуля множимого RGX

|

4

|

Загрузка.

Сдвиг в сторону старших разрядов.

|

УС1,

УС2

|

|

Регистр

модуля множителя RGY

|

6

|

Загрузка.

Сдвиг в сторону старших разрядов.

|

УС3,УС4

|

|

Регистр

модуля результата RGZ

|

10

|

Загрузка.

Установка в "0".

|

УС5,

УС6

|

|

АЛУ

|

Комбинационный

сумматор

|

-

|

|

Комбинационные

схемы

|

|

Получение

на входе АЛУ сигналов "0" или RGX в зависимости от значения yi

|

|

|

Триггер

знака множимого TX

|

|

Загрузка

|

УС7

|

|

Триггер

знака множителя TY

|

|

Загрузка

|

УС8

|

|

Триггер

знака результата TZ

|

|

Загрузка

|

УС9

|

6. Структурная схема

устройства

Работа структурной схемы АЛУ имеет вид:

Такт 1. Загрузка модулей операндов в регистры

RGX, RGY, а их знаков - в триггеры TX и TY. Сброс в "0" регистра

результата RGZ.

Такт 2. Запись знака результата в триггер TZ.

Такт 3. Сдвиг регистра RGX на один разряд влево.

Через время, равное задержке на переключение регистров и комбинационных схем,

на выходе комбинационного сумматора и, следовательно, на входе регистра RGZ

устанавливается результат X=

X•21.

Такт 4. Загрузка RGZ: Z=Z+X или Z=Z+0.

Такт 5. Сдвиг RGX на один разряд влево: X = X•21.

Сдвиг RGY на один разряд влево: i=i+1. Устройство управления проверяет условие

окончания операции: i > n. Такты (6,7), (8,9), (10,11)(12,13)(14,15) ... .

Повтор действий тактов (4,5) с анализом других значений yi.

В такте 14 в регистре RGZ формируется модуль произведения. Такт 15 используется

лишь для определения условия окончания операции умножения.

7. Временная диаграмма

управляющих сигналов

Временная диаграмма управляющих сигналов,

поступающих на арифметико-логическое устройство представлена на чертеже

01.24.006.03.

При ТИ1 подаётся сигнал на УС1, УС3, УС6. УС1

производит загрузку модулей операндов в регистр RGX. УС3 производит загрузку

модулей операндов в регистр RGY. УС6 устанавливает в «0» регистр результата RGZ

(сумматор).

При ТИ2 подаётся сигнал на УС2. УС2 производит

сдвиг регистра RGХ в сторону старших разрядов.

При ТИ3 подаётся сигнал на УС5. УС5 производит

загрузку суммы в регистр RGZ.

При ТИ4 подаётся сигнал на УС2, УС4. УС2

производит сдвиг регистра RGХ в сторону старших разрядов. УС4 производит сдвиг

регистра RGY в сторону старших разрядов. Устройство проверяет условие окончания

операции: i>0.

При ТИ (5,6), (7,8), (9,10), (11,12), … . Повтор

действий ТИ (3,4) с анализом других значения yi. При ТИ9 в регистре

RGZ формируется модуль произведения. ТИ10 используется для определения условия

окончания операции умножения.

8. Схемное решение

устройства управления

Устройство управления (УУ) - формирует и подает

во все блоки процессора в нужные моменты времени определенные сигналы

управления, обусловленные спецификой выполняемой операции и результатами

предыдущих операций; формирует адреса ячеек памяти, используемых выполняемой

операцией, и передает эти адреса в соответствующие блоки ЭВМ.

Функциональная схема устройства управления для

выполнения операции умножения на один разряд множителя с фиксированной точкой

без знака, заданных в прямом коде, начиная с младших разрядов множителя, со

сдвигом частного произведения влево представлена на чертеже 01.24.006.04.

Преобразователь адреса микрокоманды преобразует

код операции команды, присутствующей в данный момент в регистре команд, в

начальный адрес микропрограммы, реализующей данную операцию, а также определяет

адрес следующей микрокоманды выполняемой микропрограммы по значению адресной

части текущей микрокоманды.

9. Микропрограмма

выполнения команды умножения

Микропрограммирование вводит дополнительный

уровень средств программирования, нижележащий по отношению к машинному языку

компьютера, и тем самым оно позволяет определять конкретные команды машинного

языка. Подобные возможности являются неотъемлемой частью архитектуры

современных компьютеров и имеют громадное значение с точки зрения обеспечения

высоких скоростных характеристик и защиты операционных систем.

Микропрограммы размещаются в специальной

управляющей памяти очень высокого быстродействия. Они состоят из индивидуальных

микрокоманд, которые гораздо более элементарны по своей природе и более

рассредоточены по функциям, чем обычные команды машинного языка. В компьютерах,

где набор команд машинного языка реализуется при помощи микропрограммирования,

каждой команде машинного языка соответствует целая и, быть может, большая

микропрограмма. Тем самым сразу же становится очевидным, что

микропрограммирование окажется эффективным только в том случае, если

управляющая память будет обладать гораздо большим быстродействием, чем

основная.

Микропрограмма умножения двоичных чисел

приведена в таблице 8.1.

Таблица

8.1

Микропрограмма выполнения команды умножения

|

Адрес

МК

|

УС1

|

УС2

|

УС3

|

УС4

|

УС5

|

УС6

|

УС7

|

УС8

|

УС9

|

Сигнал

записи в РК

|

Адрес

след. МК

|

|

100

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

0

|

0

|

101

|

|

101

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

102

|

|

102

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

103

|

|

103

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

104

|

|

104

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

105

|

|

105

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

106

|

|

106

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

107

|

|

107

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

108

|

|

108

|

0

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

109

|

|

109

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

Х

|

По адресу МК 101 подаётся сигнал на УС9. УС9

производит запись знака в триггер TZ.

ПО адресу МК 102 подаётся сигнал на УС2. УС2

производит сдвиг регистра RGX

на один разряд.

По адресу 103 подаётся сигнал на УС5. УС5

производит загрузку RGZ:Z=Z

+X или Z=Z+0.

По адресу 104 подаётся сигнал на УС2, УС4. УС2

производит сдвиг регистра на один разряд в влево.УС4 производит сдвиг регистра RGY

на один разряд влево:i=i+1.

По адресу 105 подаётся сигнал на УС5. УС5

производит загрузку RGZ:Z=Z

+X или Z=Z+0.

По адресу 106 подаётся сигнал на УС2, УС4. УС2

производит сдвиг регистра на один разряд в влево. УС4 производит сдвиг регистра

RGY на один разряд в

лево:i=i-1.

По адресу 107 подаётся сигнал на УС5. УС5

производит загрузку RGZ:Z=Z

+X или Z=Z+0.

По адресу 108 подаётся сигнал на УС2, УС4. УС2

производит сдвиг регистра на один разряд в влево. УС4 производит сдвиг регистра

RGY на один разряд в

лево:i=i+1.

По адресу 109 подаётся сигнал на УС5. УС5

производит загрузку RGZ:Z=Z

+X или

Z=Z+0.

По адресам МК 104, 106, 108 повторяется действие

адреса МК 102.

По адресам МК 105, 107, 109 повторяется действие

адреса МК 103. При адресе МК 109 записывается сигнал в РК.

ЗАКЛЮЧЕНИЕ

Было разработано арифметико-логическое

устройство (АЛУ) которое должно подходить под ряд заданных параметров:

умножения двоичных чисел, с фиксированной точкой со знаком, представленные в

прямом коде. Исходными данными являются количество разрядов (коды чисел): Мн=4

(0.0101); Мт=6(0.101010), и алгоритм умножения: на один разряд множителя,

начинается с младших разрядов множителя, со сдвигом частного произведения

влево.

Синтез АЛУ проходит в несколько этапов:

. Был выбран метод, по которому предполагалось

выполнение операции.

. Был составлен словесный алгоритм соответствующих

действий.

. После была построена блок-схема алгоритма и

определён набор управляющих сигналов.

. Исходя из алгоритма и формата исходных данных,

был определён набор составляющих АЛУ элементов.

. Затем был определена связь между элементами и

установлен порядок функционирования устройства.

. Была построена временная диаграмма управляющих

сигналов, которые

Должны были быть поданы на АЛУ от устройства

управления.

СПИСОК ИСПОЛЬЗОВАНЫХ ИСТОЧНИКОВ

1. Архитектура

компьютера. 5-е изд. - СПб.: Питер, 2010. - 884с.

2. Спиридонов

В.В. Проектирование структур АЛУ: Учебное пособие. - СПб.: СЗПИ, 1992. - 72 с.

3. Луцик,

Ю.А. Учебное пособие по курсу «Арифметические и логические основы

вычислительной техники»/ Ю.А. Луцик.:

Минск 2004-171 с.