Проектирование комбинационных схем цифровых устройств

ВВЕДЕНИЕ

С внедрением в промышленность цифровых

технологий появилась возможность строить устройства обработки оцифрованных

сигналов вычислительным методом. Такой способ обладает рядом важных

преимуществ, таких как повышенная точность обработки, меньшая зависимость

параметров от внешних условий, а также возможность реализации таких

обрабатывающих устройств, которые невозможно или трудно было реализовать в

аналоговом виде. Одни из наиболее распространенных узлов цифровых схем -

дешифраторы. Навыки создания дешифраторов необходимы при разработке практически

любого цифрового устройства.

1. Устройство

дешифрации кодов

.1 Описание

дешифратора и структурная схема устройства

Целью задачи является

синтез устройства дешифрации кодов двоичных чисел, имеющего

«к=7» входов и «I=70»

выходов, используя стандартные промышленные

ИМС К155ИД3, .

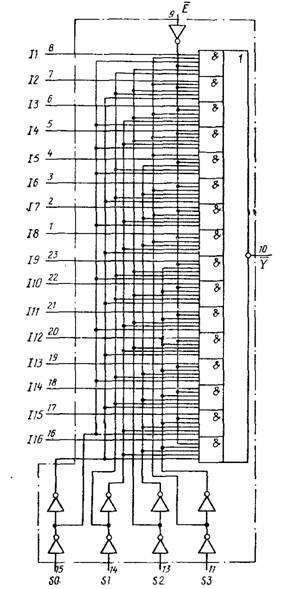

К155ИД3 - двойной

высокоскоростной дешифратор. Каждый из дешифраторов микросхемы (рис 1.1.1)

имеет 2 адресных входа А0-А1 и вход разрешения Е. Избыточные коды дают на всех

выходах высокий уровень. Выходы 0-3 взаимоисключающие, их активные выходные

уровни - низкие. Активный уровень для входа Е- низкий.

Состояния выходов дешифратора показаны в таблице

1.1.1

Таблица 1.1.1 - Состояния

выходов дешифратора 74LS154

где Н - низкий уровень, В -

высокий уровень.

Структурно-логическая схема дешифратора показана

на рисунке 1.1.1

Рисунок 1.1.1 - Структурно-логическая схема ИМС К155ИД3

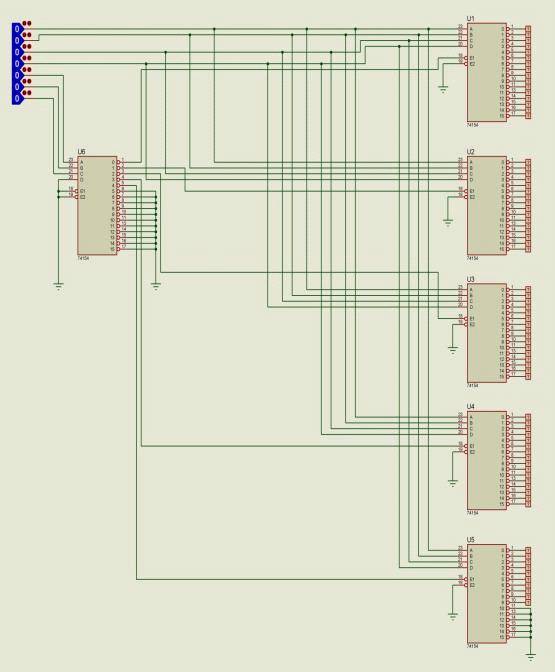

Поскольку число входов устройства k=4,

то четыре старших разряда подаются на первую ступень, которая состоит из одного

дешифратора К555ИД6. Его выходы соединяются с входами А3 каждого дешифратора

второй ступени для управления ими. Так как по заданию число выходов устройства I=70,

то необходимо использовать 5 дешифраторов для второй ступени. Четыре младших

разряда подаются на адресные входы этих дешифраторов.

Зарубежным аналогом К531ИД14 является ИМС 74LS154.

Таблица 1.1.2 - Таблица дешифрации

|

X0

|

X1

|

X2

|

X3

|

Выход

|

X0

|

X1

|

X2

|

X3

|

Выход

|

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

7

|

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

0

|

0

|

8

|

|

0

|

0

|

1

|

0

|

2

|

1

|

0

|

0

|

1

|

9

|

|

0

|

0

|

1

|

1

|

3

|

1

|

0

|

1

|

0

|

10

|

|

0

|

1

|

0

|

0

|

4

|

1

|

0

|

1

|

1

|

11

|

|

0

|

1

|

0

|

1

|

5

|

1

|

1

|

0

|

0

|

12

|

|

0

|

1

|

1

|

0

|

6

|

1

|

1

|

0

|

1

|

13

|

|

|

|

|

|

1

|

1

|

1

|

0

|

14

|

Рисунок 1.1.2 - Структурная схема устройства

дешифрации кодов

.2 Расчет

потребляемой мощности и времени задержки

По рисунку 1.1 определим общее число логических

элементов, входящих в дешифратор, - N=25.

Средняя мощность потерь одного логического элемента - Pср.пот.=10

мВт [2]. Энергопотребление одного дешифратора равно:

Так как устройство состоит из пяти дешифраторов,

то общее энергопотребление равно:

Определяем число элементов, участвующих в

распознавании одного любого слова, оно равно К=3. Находим время задержки:

Так как наше устройство двухступенчатое, то

общее время задержки передачи сигнала по одному каналу равно:

Таблица 1.2.1

- Перечень элементов

|

Позиционное

обозначение

|

Наименование

|

Количество

|

Примечание

|

|

U1;U2;U3; U4;U5 ;U6

|

ИМС К155ИД3

|

6

|

Дешифратор

|

2. Коммутатор параллельных

кодов

.1 Описание

мультиплексора и структурная схема устройства

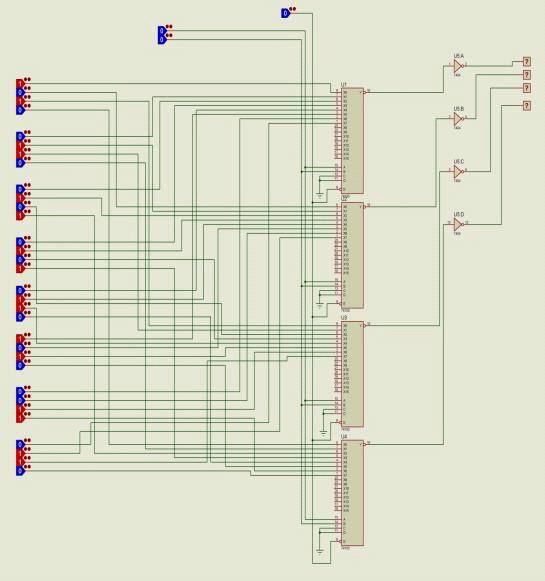

Коммутатор параллельных входов получает заданное

число слов, каждое из которых состоит из заданного количества разрядов. По

заданию число слов - 4, количество разрядов в слове - 8. Следовательно, общее

число входных бит 4*8=32. Количество адресных сигналов будет равно:

Из справочника [1] выбираем ИМС мультиплексора

К155КП1, который имеет 4 адресных входа и 16 информационных входов. Также

имеется вход разрешения, при подаче на который низкого уровня коммутации

разрешены. Этот мультиплексор позволяет передать на выход сигнал с входа, номер

которого подается на адресные входы.

Таблица 2.1.1 - Состояния выходов ИМС К155КП1

|

Входы

|

Выходы

W

|

|

Информационные

входы

|

Разрешения

S

|

|

|

D

|

C

|

B

|

A

|

|

|

|

X

|

X

|

X

|

X

|

H

|

H

|

|

L

|

L

|

L

|

L

|

L

|

E0

|

|

L

|

L

|

L

|

H

|

L

|

E1

|

|

L

|

L

|

H

|

L

|

L

|

E2

|

|

L

|

L

|

H

|

H

|

L

|

E3

|

|

L

|

H

|

L

|

L

|

L

|

E4

|

|

L

|

H

|

L

|

H

|

L

|

E5

|

|

L

|

H

|

H

|

L

|

L

|

E6

|

|

L

|

H

|

H

|

H

|

L

|

E7

|

|

H

|

L

|

L

|

L

|

L

|

E8

|

|

H

|

L

|

L

|

H

|

L

|

E9

|

|

H

|

L

|

H

|

L

|

L

|

E10

|

|

H

|

L

|

H

|

H

|

L

|

E11

|

|

H

|

H

|

L

|

L

|

L

|

E12

|

|

H

|

H

|

L

|

H

|

L

|

E13

|

|

H

|

H

|

H

|

L

|

L

|

E14

|

|

H

|

H

|

H

|

H

|

L

|

E15

|

Количество мультиплексоров соответствует

количеству разрядов в слове. На входы каждого мультиплексора подается по одному

разряду из каждого слова, номер разряда соответствует номеру мультиплексора, а

номер входа мультиплексора соответствует номеру слова. Таким образом, при

подаче какого-либо числа на адресные входы мультиплексоров на выходе будем

иметь слово, номер которого соответствует этому числу.

Рисунок 2.1.1 -

Структурно-логическая схема мультиплексора

К155КП1

дешифратор

мультивибратор коммутатор код

Таблица 2.1.2 - Таблица коммутации

|

A0

|

А1

|

А2

|

А3

|

Источник

слов

|

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

0

|

1

|

1

|

|

0

|

0

|

1

|

0

|

2

|

|

0

|

0

|

1

|

1

|

3

|

|

0

|

1

|

0

|

0

|

4

|

|

0

|

1

|

0

|

1

|

5

|

|

0

|

1

|

1

|

0

|

6

|

|

0

|

1

|

1

|

1

|

7

|

|

1

|

0

|

0

|

0

|

8

|

Рисунок 2.1.2 - Структурная схема коммутатора

параллельных кодов

Таблица 2.1.3 - Перечень элементов

|

Позиционное

обозначение

|

Наименование

|

Количество

|

Примечание

|

|

U1-U4

|

ИМС К155КП1

|

4

|

Мультиплексор

|

2.2 Расчет потребляемой

мощности и времени задержки

По структурно-логической схеме

мультиплексора К155КП1 определяем число логических элементов, входящих в состав

стандартного мультиплексора, - N=25.

Средняя потребляемая мощность одним элементом Pпот.ср

=

22 мВт. Энергопотребление одного мультиплексора равно:

В схеме используется М=5

стандартных мультиплексоров К155КП1. Общее энергопотребление всего устройства

равно:

Расчет времени задержки

осуществляется для передачи одного слова со входа коммутатора на выход для

одной ИМС мультиплексора, так как все ИМС работают во времени одновременно

(параллельно). Считается, что входные слова и стробирующие сигналы поданы на

устройства заранее, а искомая задержка определяется относительно момента подачи

адресных сигналов.

Средняя величина временной

задержки элемента равна:

По структурно-логической схеме

К155КП1 определяем количество логических элементов, участвующих в прохождении

сигнала, - К1 =4.

Задержка передачи сигнала

стандартным мультиплексором равна:

3.

Устройство параллельного ввода слов в

регистры

.1 Описание регистра

и структурная схема устройства

Устройство параллельного ввода в регистр состоит

из информационной части (регистры) и управляющей (счетчик, дешифратор). Счетчик

считает слова и отправляет номер этого слова в дешифратор, который по этой

комбинации выбирает регистр для записи слова.

По заданию необходимо записать шесть слов,

каждое из которых состоит из семи разрядов, с частотой 900 кГц.

Для записи всех слов необходимо использовать 5

регистров, способных принять не менее 12 разрядов. Для записи слов выберем

регистры марки 74198

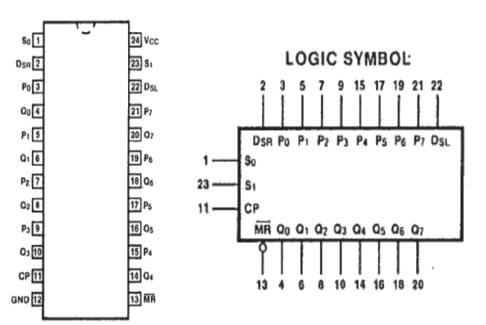

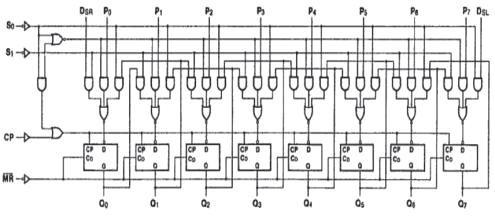

Рисунок 3.1 - Микросхема 74198

P0,

P1,

… ,P7;

− параллельные информационные входы;

Q0,

Q1,

… ,Q7;

− выходы триггеров регистра;

DSR

−

последовательный информационный вход (сдвиг разрядов вправо);

DSL

−

последовательный информационный вход (сдвиг разрядов влево);

S0,

S1

− входы выбора режима загрузки данных;

CP

−

вход для подачи тактовых импульсов;

− Master

reset (очистка регистра).

− Master

reset (очистка регистра).

Напряжение питания микросхемы составляет GHH =

+5В. Регистр имеет 8 D-триггеров, выполненных по схеме ТТЛ. Вход CP

−

динамический (управление происходит по положительному фронту). При загрузке

данных через DSL

смещение разрядов происходит справа налево, т.е. самый младший разряд

загружаемого слова будет на выходе Q0,

а самый старший - на выходе Q7.

При загрузке через вход DSR

−

наоборот. Записать данные в триггеры можно одновременно через входы P0,

P1,

… ,P7.

Рисунок 3.2 - Структура микросхемы 74198

При подаче на  лог.0

происходит очистка регистра, т.е. на все выхода будет лог.0 (таблица 3.1).

Когда S0

= 0 и S1

= 0 регистр хранит записанную информацию.

лог.0

происходит очистка регистра, т.е. на все выхода будет лог.0 (таблица 3.1).

Когда S0

= 0 и S1

= 0 регистр хранит записанную информацию.

Таблица 3.1.1 - Выбор режима загрузки данных

|

Входы

|

Функция

|

|

MR

|

CLK

|

S0

|

S1

|

|

|

0

|

X

|

X

|

X

|

Асинхронный

сброс

|

|

1

|

|

1

|

1

|

Параллельная

нагрузка

|

|

0

|

1

|

Сдвиг

вправо

|

|

1

|

|

1

|

0

|

Сдвиг

влево

|

|

1

|

X

|

0

|

0

|

Хранение

данных

|

При S0

= 1 и S1

= 1, а также по фронту на CP,

в регистр загружаются данные с входов P0,

P1,

… ,P7. Когда S0

= 0, а S1

= 1 будет происходить запись с последовательного входа DSR.

По первому положительному фронту на CP

происходит сдвиг, и состояние на входе DSR

передастся в триггер с выходом Q0.

По второму фронту состояние этого триггера передастся триггеру с выходом Q1,

а вQ0

запишется новое состояние входа DSR

и т.д. Аналогично вводятся данные с входа DSL

при S0

= 1, а S1

= 0, только в этом случае сдвиг будет происходить в обратную сторону.

В качестве счетчика выбираем микросхему 7490,

обладающую четырехразрядным выходом. Входы синхронного сброса RI и R2

(двухвходовой элемент И) запрещают действие импульсов по обоим тактовым входам

и входам установки S. Импульс, поданный на вход R, дает сброс данных по всем

триггерам одновременно.

Таблица 3.1.2 - Режим работы счётчика

7490

|

Счет

|

Выход

|

|

Q3

|

Q2

|

Q1

|

Q0

|

|

0

|

0

|

0

|

0

|

0

|

|

1

|

0

|

0

|

0

|

1

|

|

2

|

0

|

0

|

1

|

0

|

|

3

|

0

|

0

|

1

|

1

|

|

4

|

0

|

1

|

0

|

0

|

|

5

|

0

|

1

|

0

|

1

|

|

6

|

0

|

1

|

1

|

0

|

|

7

|

0

|

1

|

1

|

1

|

|

8

|

1

|

0

|

0

|

0

|

|

9

|

1

|

0

|

0

|

1

|

|

10

|

1

|

0

|

1

|

0

|

|

11

|

1

|

0

|

1

|

1

|

|

12

|

1

|

1

|

0

|

0

|

|

13

|

1

|

1

|

0

|

1

|

|

14

|

1

|

1

|

1

|

0

|

|

15

|

1

|

1

|

1

|

1

|

Таблица 3.1.3

- Перечень элементов

|

Позиционное

обозначение

|

Наименование

|

Количество

|

Примечание

|

|

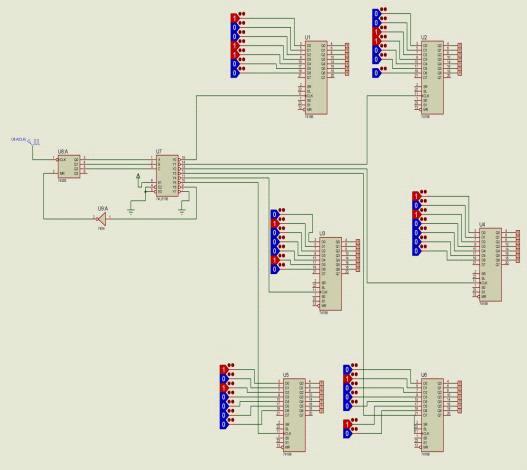

U1-U6

|

ИМС

74198

|

6

|

Регистр

|

|

U7

|

ИМС

74LS138

|

1

|

Дешифратор

|

|

U8

|

ИМС

74393

|

1

|

Счетчик

|

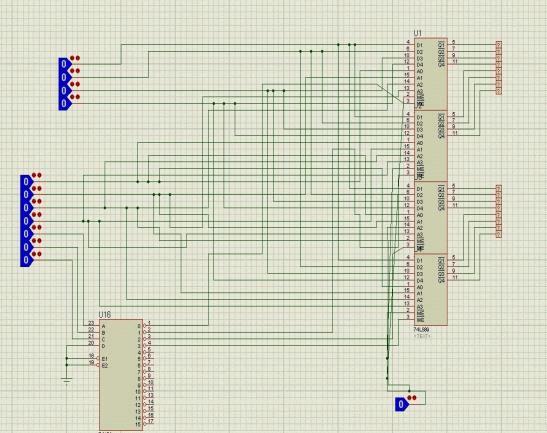

Рисунок 3.1.2 -Схема устройства параллельного

ввода слов в регистры

3.2 Расчет времени

ввода слов в регистр

Время ввода слов в регистры определяется как

произведение периода повторения импульсов ввода на число регистров в устройстве

(m=5).

Период повторения импульсов:

Время ввода всех N=6 слов за один цикл при этом

равно

. Запоминающее

устройство на ИМС оперативных ОЗУ

Запоминающее устройство

(ЗУ) выполняется на промышленной ИМС ОЗУ К531РУ8. Это статическое ОЗУ на 4

бита, имеет четыре информационных (инверсных) и четыре адресных входа, то есть

может записывать четырехразрядные двоичные числа по шестнадцати адресам. Чтение

осуществляется при подаче на вход R/W сигнала высокого уровня, запись - при подаче низкого

уровня. Исполнительный сигнал ИМС K531PY8 - сигнал CS, он подается в виде

логического нуля последним - при записи или чтении каждого слова.

Приступаем к синтезу модуля

ЗУ. По заданию нужно записать 70 слов по 4 разрядов в каждом. Поскольку в ИМС

К531РУ8 четыре информационных входа, один модуль будет состоять одного ИМС.

В один модуль можно

записать только шестнадцать слов. Для записи 70 слов нам нужно использовать

[70/16]=4 модуля.

Число адресных сигналов

определяется по формуле:

Четыре младших разряда подаются на адресные

входы всех модулей, а два старших - на управляющий дешифратор, с помощью

которого выбирается модуль для записи или чтения.

Рисунок 4.1.1 - Структурная схема запоминающего

устройства на ОЗУ К531РУ8

Таблица 4.1.1

- Таблица истинности

|

1

|

2

|

3

|

4

|

5

|

|

Комбинации

на адресных входах

|

№

ячейки в модуле

|

Номер

модуля

|

№

ячейки в общей нумерации

|

|

B,A

|

А3

А2 А1 А0

|

|

|

|

|

000

|

0000

|

0

|

0

|

0

|

|

0001

|

1

|

|

1

|

|

0010

|

2

|

|

2

|

|

0011

|

3

|

|

3

|

|

0100

|

4

|

|

4

|

|

0101

|

5

|

|

5

|

|

0110

|

6

|

|

6

|

|

0111

|

7

|

|

7

|

|

1000

|

8

|

|

8

|

|

1001

|

9

|

|

9

|

|

1010

|

10

|

|

10

|

|

1011

|

11

|

|

11

|

|

1100

|

12

|

|

12

|

|

1101

|

13

|

|

13

|

|

1110

|

14

|

|

14

|

|

1111

|

15

|

|

15

|

|

001

|

0000

|

0

|

1

|

16

|

|

0001

|

1

|

|

17

|

|

0010

|

2

|

|

18

|

|

0011

|

3

|

|

19

|

|

0100

|

4

|

|

20

|

|

0101

|

5

|

|

21

|

|

0110

|

6

|

|

22

|

|

0111

|

7

|

|

23

|

|

1000

|

8

|

|

24

|

|

1001

|

9

|

|

25

|

|

1010

|

10

|

|

26

|

|

1011

|

11

|

|

27

|

|

1100

|

12

|

|

28

|

|

1101

|

13

|

|

29

|

|

1110

|

14

|

|

30

|

|

1111

|

15

|

|

31

|

|

010

|

0000

|

0

|

2

|

32

|

|

0001

|

1

|

|

33

|

|

0010

|

2

|

|

34

|

|

0011

|

3

|

|

35

|

|

0100

|

4

|

|

36

|

|

0101

|

5

|

|

37

|

|

0110

|

6

|

|

38

|

|

0111

|

7

|

|

39

|

|

1000

|

8

|

|

40

|

|

1001

|

9

|

|

41

|

|

1010

|

10

|

|

42

|

|

1011

|

11

|

|

43

|

|

1100

|

12

|

|

44

|

|

1101

|

13

|

|

45

|

|

1110

|

14

|

|

46

|

|

1111

|

15

|

|

47

|

|

011

|

0000

|

0

|

3

|

48

|

|

0001

|

1

|

|

49

|

|

0010

|

2

|

|

50

|

|

0011

|

3

|

|

51

|

|

0100

|

4

|

|

52

|

|

0101

|

5

|

|

53

|

|

0110

|

6

|

|

54

|

|

0111

|

7

|

|

55

|

|

2

|

3

|

4

|

5

|

|

1000

|

8

|

|

56

|

|

1001

|

9

|

|

57

|

|

1010

|

10

|

|

58

|

|

1011

|

11

|

|

59

|

|

1100

|

12

|

|

60

|

|

1101

|

13

|

|

61

|

|

1110

|

14

|

|

62

|

15

|

|

63

|

|

100

|

0000

|

0

|

5

|

64

|

|

0001

|

1

|

|

65

|

|

0010

|

2

|

|

66

|

|

0011

|

3

|

|

67

|

|

0100

|

4

|

|

68

|

|

0101

|

5

|

|

69

|

|

0110

|

6

|

|

70

|

|

|

|

|

|

|

Таблица 4.2 - Перечень

элементов

|

Позиционное

обозначение

|

Наименование

|

Количество

|

Примечание

|

|

U1-U4

|

74LS89

|

4

|

ОЗУ

|

|

U16

|

74154

|

1

|

Дешифратор

|

. Ждущий мультивибратор

.1 Расчет автогенератора

Исходные данные:

Частота

автогенератора fаг=128 кГц ;

Период

повторения пусковых импульсов Тпов=4,8 мс .

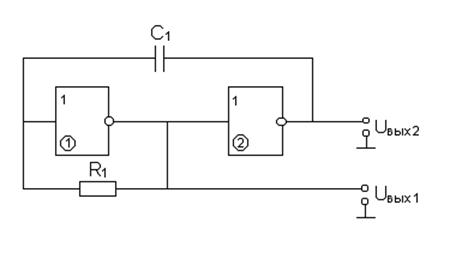

Рисунок 5.1.1 - Структурная схема автогенератора ПИ с одним

конденсатором

Период автоколебаний:

Длительность импульса на первом выходе

автогенератора:

Длительность фронта первого импульса:

Длительность импульса на втором выходе

автогенератора:

Амплитуда импульсов на обоих выходах

автогенератора

Монтажная нагрузочная емкость

При длительности фронта первого импульса  =

= можно использовать ИМС логических элементов серии 133, К155. Электрические

параметры ИМС выбранной серии:

можно использовать ИМС логических элементов серии 133, К155. Электрические

параметры ИМС выбранной серии:

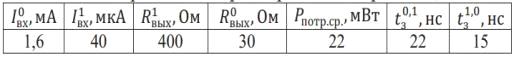

Таблица 5.1.1 - Электрические параметры ИМС

серии 133, К155

Средняя задержка микросхемы равна:

Длительность фронта импульсов автогенератора:

Сравниваем

полученное и заданное значения. Условие tф< tф1 выполняется,

выбор инверторов произведен правильно.

Определяем величину входного сопротивления

логического нуля выбранных ИМС:

где Е=5В - напряжение питания ИМС.

Сопротивление навесного резистора

автогенератора:

Где Uпор=1,5В

Из ряда номиналов резисторов и конденсаторов Е24

выбираем номинал резистора R1 = 1300 Ом.

Определяем величины скачков по фронтам

импульсов:

Первого импульса

Второго импульса

Где rд=100 Ом - сопротивление

открытого диода, встроенного в ИМС.

Находим промежуточную расчетную величину:

Находим емкость конденсатора:

Из ряда номиналов резисторов и конденсаторов Е24

выбираем номинал резистора

Проверяем правильность выбора резистора R1

и конденсатора C1:

Находим время разряда C1 через

выходную цепь элемента в состоянии «0»

и открытый

встроенный диод (rД=100 Ом)

и открытый

встроенный диод (rД=100 Ом)

Определяем время, отводимое для перезаряда С1

входными и выходными токами первого логического элемента автогенератора:

Эквивалентная постоянная времени перезаряда

равна:

Находим реальное время, необходимое для

перезаряда С1 указанными токами:

где напряжение открывания диода Uдо=0,6B

Сравниваем величины z и y - они должны

отличаться в пределах 10%:

Требуемое условие не выполняется, в этом случаи

уменьшим номинал выбранного резистора, пусть R1

= 510 Ом.

Из ряда номиналов резисторов и конденсаторов Е24

выбираем номинал резистора

Теперь условие выполняется, значит, выбранные

номиналы R1

= 510 Ом

, подойдут.

, подойдут.

5.2 Расчет делителя

частоты

Коэффициент деления частоты:

Разобьем КДЧ на простые сомножители:

В этой формуле  −

коэффициенты деления частоты каскадов делителя частоты, в роли которых

выступают ИМС счетчиков:

−

коэффициенты деления частоты каскадов делителя частоты, в роли которых

выступают ИМС счетчиков:

К555ИЕ2 (SN74LS90) - для  =

10 либо

=

10 либо  =

5

=

5

К155ИЕ4 (SN74LS92) - для,  =

12 либо

=

12 либо  =

6

=

6

К555ИЕ5 (SN74LS93) - для  =

16 либо

=

16 либо  =

4,

=

4,  =

8

=

8

Тогда ДЧ будет состоять из двух микросхем

К155ИЕ4 (SN74LS92)и трех микросхем К555ИЕ2 (SN74LS90).

Микросхема

К155ИЕ4 - четырехразрядный двоичный счетчик-делитель на 2, на 6 и на 12.

Счетчик состоит из двух независимых делителей. Если тактовая последовательность

с частотой f подана на вход  (вывод 14), на

выходе Q0 (вывод 12) получим меандр с частотой f/2. Последовательность с частотой f на тактовом

входе

(вывод 14), на

выходе Q0 (вывод 12) получим меандр с частотой f/2. Последовательность с частотой f на тактовом

входе  (вывод 1) запускает делитель

на 6, и меандр с частотой f/6 появляется на выходе Q3 (вывод 8). На

выводы

R1 и R2

подаются команды сброса. Чтобы построить

счетчик с модулем деления 12, требуется соединить делители на 2 и на 6, замкнув выводы 12 и 1. На

вход

(вывод 1) запускает делитель

на 6, и меандр с частотой f/6 появляется на выходе Q3 (вывод 8). На

выводы

R1 и R2

подаются команды сброса. Чтобы построить

счетчик с модулем деления 12, требуется соединить делители на 2 и на 6, замкнув выводы 12 и 1. На

вход  подается

входная частота f, на выходе Q3 получается последовательность симметричных прямоугольных импульсов с частотой f/12.

подается

входная частота f, на выходе Q3 получается последовательность симметричных прямоугольных импульсов с частотой f/12.

Микросхема К555ИЕ2 представляет

собой счетчик-делитель на 2, на 5 и на 10. Каждая ИС состоит из четырех

JK-триггеров. Для получения делителя на 10 выход Q0 соединяется с входом  .

.

Микросхема

К555ИЕ5 представляет

собой счетчик-делитель на 2, на 8 и на 16. Для получения делителя на 16 выход

Q0 соединяют с входом  .

.

Диаграмма выходного сигнала ДЧ представляет

собой последовательность прямоугольных импульсов, период повторения которых

равен периоду пусковых импульсов.

Рисунок 5.2.1 - Диаграммы напряжений сигнала и

выходных сигналов ДЧ, использующих в последнем каскаде указанные ИМС счетчиков

5.3 Расчет

формирователя коротких пусковых импульсов

Для запуска ждущего генератора ПИ требуются

короткие пусковые импульсы, длительность которых не меньше, чем (3 ÷

5)tз.ср.

Поэтому на основе импульсов, полученных делителем частоты, нужно получить

пусковые.

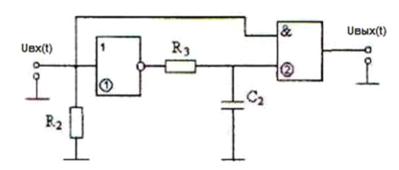

Рисунок 5.3.1 - Структурная схема формирователя

коротких пусковых импульсов

Исходные данные для расчета:

Длительность выходного импульса: tи

вых=0,5 мкс

Длительность входного импульса:tи

вх=0,67

мкс

Период повторения выходных импульсов:Твх=Тпуск=15

мс

Требуемая длительность фронта выходных

(пусковых) импульсов:

Для формирователя можно использовать логические

элементы той же серии, что и для автогенератора ПИ (серии 133, К155). Поскольку

элементы выбраны той же серии, то

Сопротивление R3 находится как:

Где

Из ряда E24 выбираем

Определяем емкость конденсатора:

где  ;

; .

.

В соответствии с рядом E24 выберем

Определяем время восстановления напряжения на

конденсаторе:

Проверим условие восстановления

Так как условие выполняется, то выбранные

номиналы ,

,

подойдут.

подойдут.

5.4 Расчет ждущего

генератора ПИ

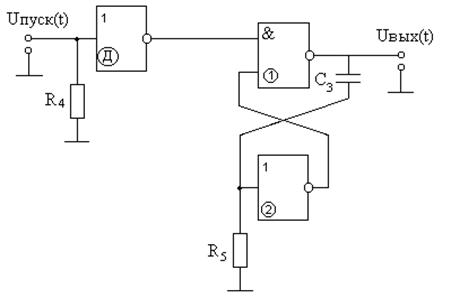

Рисунок 5.4.1 - Структурная схема ждущего

генератора ПИ

Элементы дополнительный (Д) и второй -

инверторы, первый логический элемент выполняет функцию 2И-НЕ.

Исходные данные:

Период повторения пусковых импульсов: ;

;

Длительность выходных импульсов: ;

;

Амплитуда выходных импульсов:  .

.

Требуемую длительность фронта выходных

импульсов:

При такой длительности фронта можно использовать

ИМС серии 134, К158

Таблица 5.4.1 - Электрические параметры ИМС

серии 134, К158

Определяем величину входного сопротивления

логического нуля выбранных ИМС:

Сопротивление подключенного ко входам логических

элементов R4=R5:

где Uпор=1,5В

Из ряда номиналов резисторов и конденсаторов Е24

выбираем номинал резистора

Определяем постоянное смешение на входах

логических элементов:

Рассчитываем амплитуду выходного импульса:

Находим промежуточную расчетную величину:

А затем емкость конденсатора:

Из ряда номиналов резисторов и конденсаторов Е24

выбираем номинал конденсатора

Определим время восстановления напряжения на

конденсаторе:

Проверим выполнение условия:

Условие выполняется, значит, выбранные номиналы:

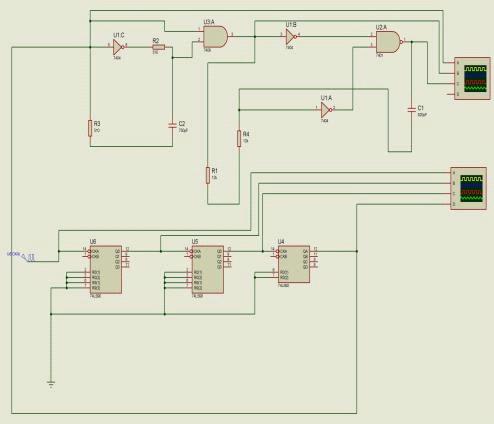

.5 Схема ждущего мультивибратора

Рисунок 5.5.1 - Принципиальная схема ждущего

мультивибратора

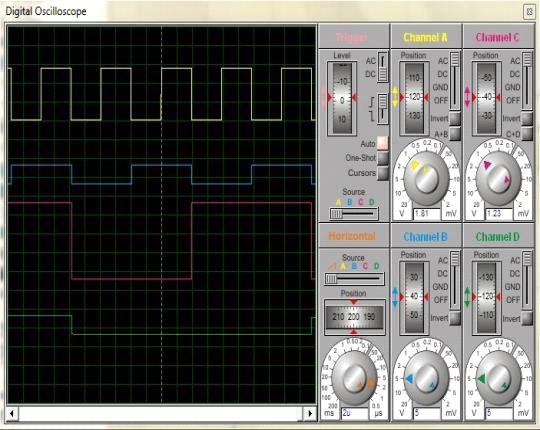

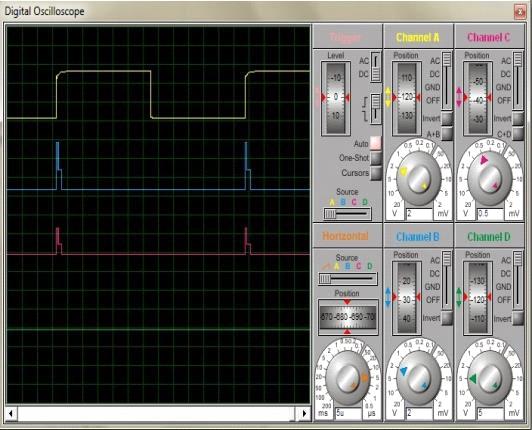

Рисунок 5.5.2 - Диаграммы напряжений всего

устройства

Таблица 5.5.1 - Перечень элементов

|

Позиционное

обозначение

|

Наименование

|

Количество

|

|

U4(C-E)

|

Инвертор

7404

|

3

|

|

DD1,DD2

|

Счетчик

74LS90

|

2

|

|

DD3

|

Счетчик 74LS92

|

1

|

|

DD4

|

Элемент

И 7408

|

1

|

|

DD5

|

Элемент

И-НЕ 7401

|

1

|

|

C3

|

Конденсатор

820 пФ

|

1

|

|

C2

|

Конденсатор

750 пФ

|

1

|

|

R2, R3

|

Резистор

510 Ом

|

2

|

|

R4, R5

|

Резистор

12 кОм

|

2

|

ЗАКЛЮЧЕНИЕ

В данной курсовой работе были отработаны навыки

использования пакета программ для автоматизированного проектирования

электронных схем Proteus.

В частности использование Proteus

для построения принципиальных схем, на основе пяти представленных задач.

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ

1. В.Л.

Шило. Популярные цифровые микросхемы: Справочник. М. - Радио и связь, 1987 -

352 с.

2. Методические

указания по выполнению курсовой работы по дисциплине "Цифровые устройства

и микропроцессоры", Л.В. Просвирякова. - 16 с.

. Букреев

И., Горячев В., Мансуров Б. Микроэлектронные схемы цифровых устройств, 2009 г.

- 712 с.