Создание цифровых устройств

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ПОЛИТЕХНИЧЕСИЙ УНИВЕРСИТЕТ

Курсовая работа

дисциплина: Цифровые устройства и

микропроцессоры

Выполнил: Скобликов

Группа: 33422/1

Преподаватель: Бунтов В.Д.

Вариант: 1.2 (а)

Санкт - Петербург

г

Содержание

1. Обзор методов решения

.1 Построение устройства на микросхемах малой степени

интеграции

.2 Реализация булевых функций на мультиплексорах

.3 ПЗУ

.4 ПЛМ

. Реализация на микросхемах малой степени интеграции

. Реализация на микросхемах средней степени интеграции

. Реализация на ПЗУ

. Реализация на ПЛМ

Заключение

. Обзор

методов решения

.1

Построение устройства на микросхемах малой степени интеграции

Существует много типов микросхем ТТЛ малой степени интеграции,

различающихся по функциональному назначению, нагрузочной способности, схеме

выходного каскада. Работа логических элементов этих микросхем достаточно

проста. Для элементов И выходной уровень 1 формируется при подаче на все входы

элемента уровней 1, для элемента ИЛИ для формирования уровня 1 на выходе

достаточно подачи хотя бы на один вход уровня 1. Элементы И-НЕ (основной

элемент серий ТТЛ) и ИЛИ-НЕ дополнительно инвертируют выходной сигнал, элемент

И-ИЛИ-НЕ состоит из нескольких элементов И, выходы которых подключены к входам

элемента ИЛИ-НЕ. [4, стр. 20]

.2

Реализация булевых функций на мультиплексорах

Мультиплексор - устройство, которое в зависимости от кода на адресных

входах осуществляет выбор одного из информационных входов и направленную

передачу сигнала на выход.

Мультиплексоры могут быть использованы для синтеза КУ, реализующих

логические функции многих переменных. В ряде случаев, особенно при большом

числе входных переменных и значительном количестве выходов это позволяет

уменьшить общее число требуемых корпусов микросхем.

КУ на мультиплексорах синтезируют исходя из карты Карно заданной функции.

Число информационных входов мультиплексора выбирают равным числу клеток карты

Карно. Если двоичные коды на адресных входах мультиплексора и коды клеток карт

Карно совпадают, а информационные сигналы определяются значениями 0 или 1,

записанными в клетках, то такой мультиплексор полностью воспроизводит заданное

КУ. [1, стр. 51-58]

.3 ПЗУ

ПЗУ представляет собой большую интегральную схему (БИС), имеющую N входов и М выходов. На входе схемы

установлен дешифратор, преобразующий комбинации двухразрядного двоичного кода в

четырехпозиционный унитарный (десятичный) код. При каждой комбинации входного

ДК на одном из выходов дешифратора появляется логическая 1, а на остальных -

нули.

Между выходами дешифратора k, l, m, n и выходными

шинами ПЗУ X, Y, Z включены цепочки

из двух последовательно включенных диодов VD1 и VD2. В

исходном состоянии цепочки, связывающие выходы дешифратора и выходы ПЗУ, ток не

проводят, и связи между шинами k, l, m, n и Х, Y, Z отсутствуют. При этом со всех выходов X, Y, Z снимаются

логические нули.

Пользователь на специальном устройстве - программаторе - создает нужные

связи между шинами, подавая пробивные напряжения между определенными точками.

При этом соответствующие диоды пробиваются, и в дальнейшем могут

рассматриваться как короткозамкнутые.

На ПЗУ можно реализовать нужную таблицу истинности комбинационного

устройства, имеющего несколько выходов. Одна схема ПЗУ может заменить большое

число логических микросхем малого и среднего уровня интеграции, поэтому ПЗУ

могут эффективно использоваться для создания сложных комбинационных устройств.

Кроме того, ПЗУ находят широкое применение как элементы постоянной памяти, в

которые заносятся программы, управляющие работой микропроцессоров и однокристальных

микроЭВМ. [2, стр. 154]

.4 ПЛМ

Программируемые логические матрицы (ПЛМ) как и ПЗУ относятся к

программируемым ИС двухступенчатой структуры, состоящей из двух

последовательных матриц «Матрица И - матрица ИЛИ». ПЛМ отличается от ПЗУ тем,

что в ПЗУ матрица И жесткая, а матрица ИЛИ программируемая, а в ПЛМ обе матрицы

И и ИЛИ программируемые. Второе отличие состоит в том, что на ПЛМ можно

реализовать не любую систему переключательных функций, как на ПЗУ, а лишь

удовлетворяющую дополнительному ограничению: длина дизъюнктивных нормальных

форм воспроизводимых функцией не должна превышать числа переходных цепей между

матрицами И и ИЛИ.

Структурная схема ПЛМ состоит из входных и выходных буферных каскадов и

матрицы элементов И и ИЛИ. Входные буферы разгружают входные цепи и преобразуют

однофазные входные сигналы в парафазные. Выходные буферы обеспечивают

необходимую нагрузочную способность ПЛМ и стробируют ее с помощью входа выборки

кристалла ВК, сигнал на котором либо разрешает работу ПЛМ, либо переводит

выходы в состояние «Отключено».

Основными параметрами ПЛМ являются число входов , число переходных цепей (термов) и число выходов . Структура матрицы И и ИЛИ состоит из горизонтальных и

вертикальных шин, в узлах пересечения которых находятся элементы связи (ЭС),

которые при программировании вводятся или устраняются.

ПЛМ широко используются, как и ПЗУ, для реализации переключательных

функций преобразования кодов, так и в

качестве управляющей памяти ЭВМ с микропрограммным управлением. Следует

отметить, что ПЗУ реализует наиболее развернутые формы представления функций

(СДНФ) и для них не используется минимизация функций. Для ПЛМ реализуемую

систему функций следует минимизировать. [4,

стр. 226]

Построить устройство, реализующее 4 логических функции:

F1 = ABC E

E + AE

+ AE + ACD +

+ ACD +

=

AB

=

AB

+ A

+ A

+

+

+

EF= ABCDE

+

EF= ABCDE + AB

+ AB

+

+

D

+ ABD4 = AB

D

+ ABD4 = AB

+

+  E

E +

+

+ C

+ C + EF

+ EF

Для

начала следует упростить логические функции, это можно сделать двумя методами:

методом Квайна и методом Карно. Пользоваться методом Квайна в данной ситуации

затруднительно, поэтому будем использовать метод Карно.

1. Упростим каждую из четырех функций.

F1 = ABC E

E + AE

+ AE + ACD +

+ ACD +

Составим

карту Карно:

|

F1

|

000

|

001

|

011

|

010

|

110

|

111

|

101

|

100

|

|

D̅E̅F̅

|

D̅E̅F

|

D̅EF

|

D̅EF̅

|

DEF̅

|

DEF

|

DE̅F

|

DE̅F̅

|

|

000

|

A̅B̅C̅

|

1

|

1

|

1

|

1

|

|

|

|

|

|

001

|

A̅B̅C

|

1

|

1

|

1

|

1

|

|

|

|

|

|

011

|

A̅BC

|

|

|

|

|

|

|

|

|

|

010

|

A̅BC̅

|

|

|

|

|

|

|

|

|

|

110

|

ABC̅

|

|

|

|

1

|

1

|

|

|

|

|

111

|

ABC

|

|

|

|

1

|

1

|

1

|

1

|

1

|

|

101

|

AB̅C

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

|

100

|

AB̅C̅

|

1

|

1

|

1

|

1

|

1

|

|

|

|

Стоит отметить, что склеивание для функции шести переменных выполняется

также и для клеток, кодировка которых отличается значениями одного из

аргументов, но не расположенных рядом.

И того, минимизируя формулу получим:

F1 =B̅D̅+AEF̅+ACD.

Рассмотрим следующую функцию F2:

F2 = AB

+ A

+ A

+

+

+ EF

+ EF

Составим

карту Карно:

|

F2

|

000

|

001

|

011

|

010

|

110

|

111

|

101

|

100

|

|

D̅E̅F̅

|

D̅E̅F

|

D̅EF

|

D̅EF̅

|

DEF̅

|

DEF

|

DE̅F

|

DE̅F̅

|

|

000

|

A̅B̅C̅

|

1

|

1

|

1

|

1

|

|

1

|

|

|

|

001

|

A̅B̅C

|

1

|

1

|

1

|

1

|

|

1

|

|

|

|

011

|

A̅BC

|

|

|

1

|

|

|

1

|

|

|

|

010

|

A̅BC̅

|

|

|

1

|

|

|

1

|

|

|

|

110

|

ABC̅

|

1

|

1

|

1

|

1

|

|

1

|

|

1

|

|

111

|

ABC

|

1

|

|

1

|

|

|

1

|

|

1

|

|

101

|

AB̅C

|

1

|

1

|

1

|

1

|

|

1

|

|

|

|

100

|

AB̅C̅

|

1

|

1

|

1

|

1

|

|

1

|

|

|

Как видно из таблицы, минимизировать функцию не удастся, придется

оставить все как есть.

F2 = AB

+ A

+ A

+

+

+

EF

+

EF

Функция F3:

3

= ABCDE + AB

+ AB

+

+

D + ABD

D + ABD

Составим

карту Карно:

|

F3

|

000

|

001

|

011

|

010

|

110

|

111

|

101

|

100

|

|

D̅E̅F̅

|

D̅E̅F

|

D̅EF

|

D̅EF̅

|

DEF̅

|

DEF

|

DE̅F

|

DE̅F̅

|

|

000

|

A̅B̅C̅

|

|

|

|

|

1

|

1

|

1

|

1

|

|

001

|

A̅B̅C

|

|

|

|

|

|

|

|

|

|

011

|

A̅BC

|

|

|

|

|

|

|

|

|

|

010

|

A̅BC̅

|

|

|

|

|

1

|

1

|

1

|

1

|

|

110

|

ABC̅

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

|

111

|

ABC

|

|

|

|

|

1

|

1

|

1

|

1

|

|

101

|

AB̅C

|

|

|

|

|

|

|

|

|

|

100

|

AB̅C̅

|

|

|

|

|

|

|

|

|

Объединим клетки строки ABC̅,

затем строки

A̅B̅C̅D и A̅BC̅D, так

как они отличаются значением только одного аргумента, аналогично объединим ABC̅D и ABCD.

Получим F3 =A̅C̅D+ABD+ABC̅

;

Перейдем к F4

F4 = AB

+

+  E

E +

+

+ C

+ C + EF ;

+ EF ;

Карта

Карно:

|

F3

|

000

|

001

|

011

|

010

|

110

|

111

|

101

|

100

|

|

D̅E̅F̅

|

D̅E̅F

|

D̅EF

|

D̅EF̅

|

DEF̅

|

DEF

|

DE̅F

|

DE̅F̅

|

|

000

|

A̅B̅C̅

|

1

|

1

|

1

|

1

|

1

|

1

|

|

|

|

001

|

A̅B̅C

|

1

|

1

|

1

|

1

|

1

|

1

|

|

|

|

011

|

A̅BC

|

1

|

1

|

1

|

1

|

1

|

1

|

|

|

|

010

|

A̅BC̅

|

|

|

1

|

1

|

1

|

1

|

|

|

|

110

|

ABC̅

|

1

|

1

|

1

|

|

|

1

|

|

|

|

111

|

ABC

|

1

|

1

|

1

|

1

|

|

1

|

|

|

|

101

|

AB̅C

|

1

|

1

|

1

|

1

|

|

1

|

|

|

|

100

|

AB̅C̅

|

1

|

1

|

1

|

1

|

|

1

|

|

|

F4 =B̄D̄+CD̄+AD̄E+EF+A̅E

В итоге получили:

F1 =B̅D̅+AEF̅+ACD

F2 = ABE̅F̅+ AC̅D̅+B̅D̅+EF

F3 =A̅C̅D+ABD+ABC̅

F4 =B̅D̅+CD̅+AD̅E+EF+A̅E

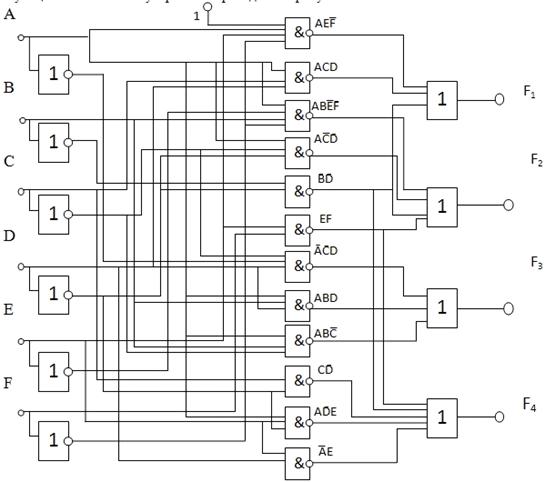

2. Реализация на микросхемах малой степени интеграции

Функциональная схема устройства приведена на рисунке 1.

Рисунок 1

элементов «И-НЕ» 4 элемента «ИЛИ» 6 элементов «НЕ» 1х7421-два четрех

входовых И-НЕ (74ALS21 t=11нс I=0.9мА), 2х7412-три трехвходных И-НЕ(74ALS12 t=25нс I=0.8мА),

1х7409-четыре двухвходовых И-НЕ(t=18нс

I=15мА), 1х7427 - три трехводных

И-НЕ(74ALS27 t=4.75нс I=3.6мА),

1х7425-два пятивходных ИЛИ(t=10нс

I=9мА), 1х7404-шесть инверторов (74ALS04 t=2нс I=6мА),

1х7427-три трехводных ИЛИ( t=4.75,

W=3.6).

W=57,75мВт

t=46нс

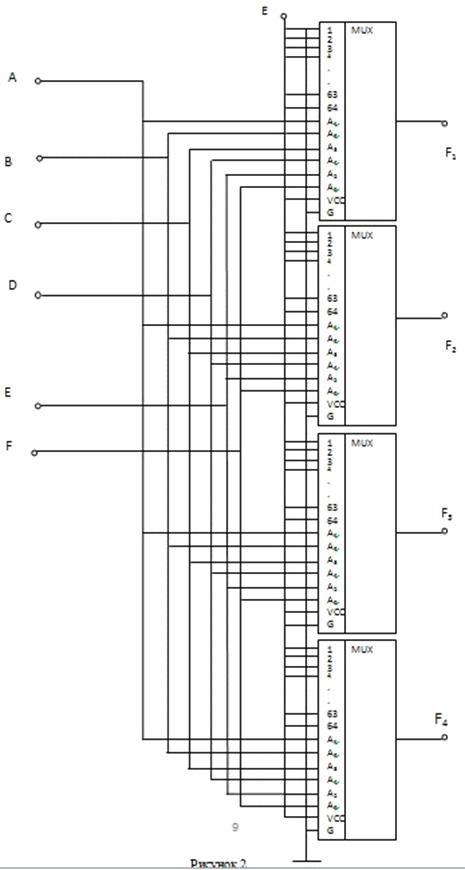

3. Реализация на микросхемах средней степени интеграции

Реализация

на 64-входовых мультиплексорах

На адресные входы мультиплексора A1, A2, A3, A4, A5, A6 подаются соответственно входные

логические переменные A, B, C, D, E, F а на информационных входах 1-64 зафиксированы значения

реализуемой логической функции на наборах логических переменных (см. таблицу

истинности), номера которых совпадают с номерами информационных входов

мультиплексора. На рисунке 2 изображена функциональная схема устройства.

Таблица истинности:

|

A

|

B

|

C

|

D

|

E

|

F

|

F1

|

F2

|

F3

|

F4

|

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

0

|

|

0

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

1

|

1

|

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

|

0

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

|

0

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

|

0

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

1

|

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

|

0

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

0

|

|

0

|

1

|

0

|

1

|

1

|

0

|

0

|

0

|

1

|

1

|

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

|

0

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

|

0

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

1

|

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

|

0

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

0

|

|

0

|

1

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

|

0

|

1

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

1

|

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

0

|

0

|

|

1

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

0

|

0

|

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

|

1

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

0

|

1

|

|

1

|

0

|

1

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

|

1

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

0

|

1

|

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

0

|

0

|

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

|

1

|

1

|

0

|

0

|

0

|

0

|

0

|

1

|

1

|

0

|

|

1

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

|

1

|

1

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

|

1

|

1

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

|

1

|

1

|

0

|

1

|

0

|

0

|

0

|

1

|

1

|

0

|

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

0

|

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

|

1

|

1

|

1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

|

1

|

1

|

1

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

|

1

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

1

|

|

1

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

0

|

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

0

|

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

0

|

1

|

0

|

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

Стоит отметить, что 64 входовой мультиплексор не производят, поэтому его

придется собрать из шестнадцати входовых мультиплексоров. Это схема немного

упрощена в силу своих больших размеров. И того в схеме средней интеграции будем

иметь 16 шестнадцати входовых мультиплексоров и 4 четырехвходовых, в данном

случае это не лучший способ реализации. 64-входовой мультиплексор изображен на

рисунке 3.

F

Рисунок 3. Мультиплексор на 64 входа

16х74159-шестнадцативходовой

мультиплексор ( t=24нс I=34 мА)

4х74155 -четырехвходовой мультиплекор (t=13нс I=25мА)

W=785мВт

t=93нс.

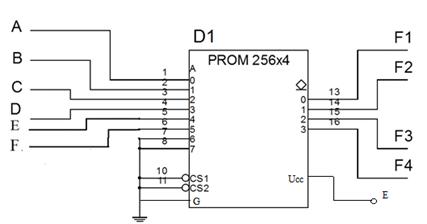

4. Реализация на ПЗУ

Функциональная схема устройства на ПЗУ приведена на рисунке 4.

Рисунок 4

В качество ПЗУ можно использовать К155РЕ21, t=30нс W=682,5

мВт

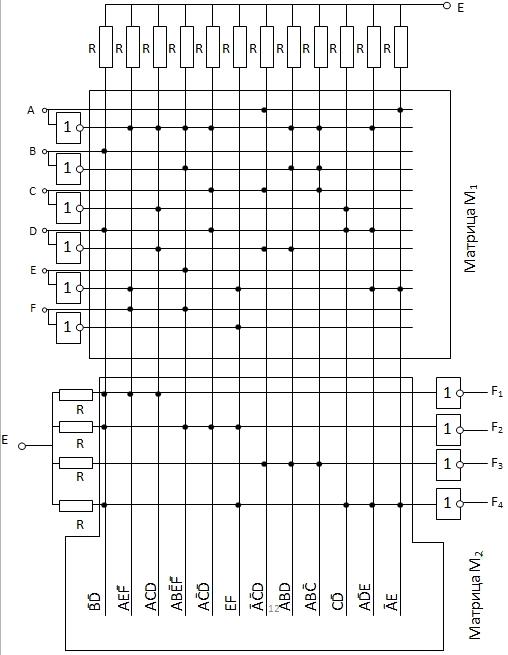

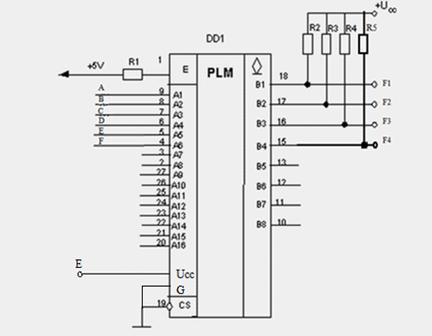

5. Реализация на ПЛМ

Входные

переменные А, В, С, D, E, F и их инверсии поступают в горизонтальные шины матрицы

М1, а вертикальные шины формируют конъюнкции:  CD, A

CD, A

,

,  CD,

CD,  B, A, B, C, A

B, A, B, C, A ,

,  D, C

D, C , A

, A D,

D,  C. Связи между

вертикальными и горизонтальными шинами, введенные при программировании,

позволяют формировать конъюнкции в логических элементах И. Элементы матрицы М2

формируют на выходе требуемые логические суммы. Функциональная и принципиальная

схемы показаны на рисунке 6 и 7

C. Связи между

вертикальными и горизонтальными шинами, введенные при программировании,

позволяют формировать конъюнкции в логических элементах И. Элементы матрицы М2

формируют на выходе требуемые логические суммы. Функциональная и принципиальная

схемы показаны на рисунке 6 и 7

Рисунок

6

Рисунок

7

В

качестве ПЛМ можно использовать КР556РТ22 t=20 нс W=780

мВт.

Заключение

мультиплексор логический матрица микросхема

Заданные

нам функции лучше реализовывать на ПЛМ, в этом случае мы получим наибольшее

быстродействие t=20нс, при этом будет использован всего 1 корпус,

потребляемая мощность равна 780 мВт.

Таблица

1

|

Реализация на микросхемах малой степени интеграции

|

|

Использовано корпусов

|

Время задержки, нс

|

Потребляемая мощность, мВт

|

|

8

|

46

|

57,75

|

|

Реализация на микросхемах средней степени интеграции

|

|

36

|

99

|

675

|

|

Реализация на ПЗУ

|

|

1

|

30

|

682,5

|

|

Реализация на ПЛМ

|

|

1

|

20

|

780

|

Литература:

1. Бунтов В.Д., Макаров С.Б. Микропроцессорные системы,

часть 1 Цифровые устройства.

. Сайт http://www.microshemca.ru/

. Бирюков С.А. Применение цифровых микросхем серий ТТЛ

и КМОП. - М.: ДМК Пресс. - 240 с.: ил. (В помощь радиолюбителю).

. Горбачев Г.Н., Чаплыгин Е.Е. Промышленная

электроника: Учебник для вузов/Под ред. В.А. Лабунцова. - М.: Энергоатом-издат,

1988, - 320 с.