Реализация синхронного автомата на интегральных микросхемах

КУРСОВАЯ

РАБОТА

по

дисциплине «Схемотехника ЭВМ»

Тема работы

Реализация

синхронного автомата на интегральных микросхемах

СОДЕРЖАНИЕ

Введение

.

Анализ задания на курсовой проект

.

Выбор микросхемы регистра сдвига

.

Методика отладки модели УСПБ

.1

Генератор слов

.2

Логический анализатор

.

Выбор микросхемы для реализации блока индикации

Заключение

Список

литературы

ВВЕДЕНИЕ

Объектом разработки и реализации является

устройство селекции бинарной подпоследовательности символов (УСБП) из бесконечной

бинарной последовательности (ББП). Такого рода устройства используются в

телекоммуникационных системах (в том числе, в вычислительных сетях, сотовых

телефонах и т.п.). Задачей УСБП является выделение подпоследовательности

двоичных символов заданной длины и строго определенной структуры из бесконечной

последовательности. После селекции заданной подпоследовательности может

производиться дополнительная целенаправленная обработка некоторой совокупности

последующих бинарных символов.

В курсовом проекте необходимо разработать УСБП,

которое после обнаружения заданной подпоследовательности символов принимает

следующие подряд восемь символов, проверяет их на заданное условие и, в случае

выполнения этого условия, отображает их содержимое на двух семисегментных индикаторах,

интерпретируя содержимое этих восьми символов как двухразрядный

шестнадцатиричный код. После этого устройство циклически переходит в режим

обнаружения заданной подпоследовательности, приёму последующих восьми бит, их

анализу и, возможно, индикации их содержимого. Информация о заданном содержимом

восьми бит должна сохраняться (и отображаться) до следующей селекции заданной

подпоследовательности.

1. АНАЛИЗ ЗАДАНИЯ НА КУРСОВОЙ ПРОЕКТ

Объектом разработки и реализации является

устройство селекции бинарной подпоследовательности символов (УСБП) из

бесконечной бинарной последовательности (ББП). Такого рода устройства

используются в телекоммуникационных системах (в том числе, в вычислительных

сетях, сотовых телефонах и т.п.). Задачей УСБП является выделение

подпоследовательности двоичных символов заданной длины и строго определенной

структуры из бесконечной последовательности. После селекции заданной

подпоследовательности может производиться дополнительная целенаправленная

обработка некоторой совокупности последующих бинарных символов.

В курсовом проекте необходимо разработать УСБП,

которое после обнаружения заданной подпоследовательности символов принимает

следующие подряд восемь символов, проверяет их на заданное условие и, в случае

выполнения этого условия, отображает их содержимое на двух семисегментных

индикаторах, интерпретируя содержимое этих восьми символов как двухразрядный

шестнадцатиричный код. После этого устройство циклически переходит в режим

обнаружения заданной подпоследовательности, приёму последующих восьми бит, их

анализу и, возможно, индикации их содержимого. Информация о заданном содержимом

восьми бит должна сохраняться (и отображаться) до следующей селекции заданной

подпоследовательности.

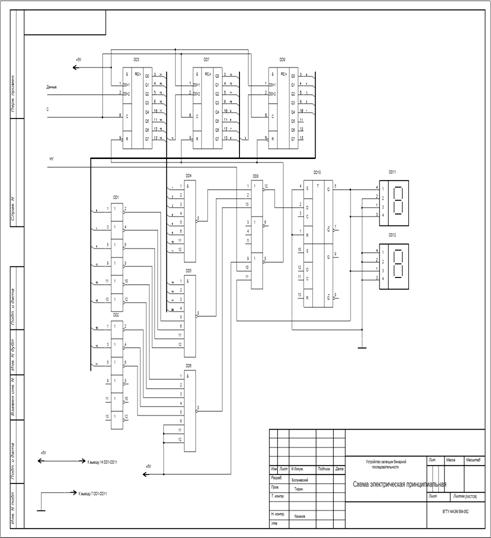

На рис. 1 разрабатываемое устройство представлено

на уровне «черного ящика», где обозначено:

xi

- i-ый символ

бесконечной последовательности;

с - сигнал синхронизации, сопровождающий символ;

y1…y4

- первые четыре бинарных символа, непосредственно следующие за выделенной

подпоследовательностью;

y5…y8

- вторые четыре бинарных символа, непосредственно следующие за выделенной

подпоследовательностью;

HG1, HG2

- соответственно, первый и второй семисегментный индикатор (использовать

семисегментные индикаторы с общим катодом!).

Рисунок 1

На рисунке 2 представлена временная диаграмма,

поясняющая принцип работы УСБП.

Рисунок 2

Как следует из временной диаграммы, смена

символа в бесконечной последовательности происходит по фронту сигнала

синхронизации (с), а его срез соответствует стабильному значению символа

последовательности, т.е. по срезу сигнала синхронизации должно фиксироваться и

анализироваться значение символа в устройстве селекции бинарной подпоследовательности.

Для примера будем полагать, что символы x1…

x6

образуют заданную для селектирования подпоследовательность, при этом символ x1

является первым в искомой подпоследовательности, а символ x6

- последним. Состояние символов x7…

x10,

непосредственно следующих за выделяемой подпоследовательностью,

интерпретируется как шестнадцатиричный код. Этот код необходимо запомнить в

УСБП, проверить на заданное условие и отобразить состояние этих символов

соответствующим символом на семисегментном индикаторе (в качестве примера

анализируется состояние только четырех символов, а в курсом проекте должны

анализироваться и индицироваться состояния восьми символов!). При этом символ x7

должен интерпретироваться как младший разряд шестнадцатиричного кода, а символ x10

как старший его разряд. В таблице 1 показано соответствие шестнадцитиричного

кода и семисегментного символа.

Таблица

1

|

x10

|

x9

|

x8

|

x7

|

Семисегм.

иникатор

|

x10

|

x9

|

x8

|

x7

|

Семисегм.

иникатор

|

|

0

|

0

|

0

|

0

|

1 1

|

0

|

0

|

0

|

|

|

|

0

|

0

|

0

|

1

|

1 1

|

0

|

0

|

1

|

|

|

|

0

|

0

|

1

|

0

|

1 1

|

0

|

1

|

0

|

|

|

0

|

0

|

1

|

1

|

1 1

|

0

|

1

|

1

|

|

|

|

0

|

1

|

0

|

0

|

1 1

|

0

|

0

|

0

|

|

|

|

0

|

1

|

0

|

1

|

1 1

|

1

|

0

|

1

|

|

|

|

x10

|

x9

|

x8

|

x7

|

Семисегм.

иникатор

|

x10

|

x9

|

x8

|

x7

|

Семисегм.

иникатор

|

|

0

|

1

|

1

|

0

|

1 1

|

1

|

1

|

0

|

|

|

|

0

|

1

|

1

|

1

|

1 1

|

1

|

1

|

1

|

|

|

Таким образом, как следует из рассматриваемого

примера, УСБП должно выделить заданную подпоследовательность символов x1…

x6

(т.е. последовательный код 011101), принять четыре последующих символа x7…

x10

(их шестнадцатиричный код 0110),сравнить этот код с заданным и, в случае их

совпадения, отобразить этот код на семисегментном индикаторе. Код символов x7…

x10

должен индицироваться до следующего их выделения, а УСБП после начала индикации

должно автоматически возобновить выделение заданной подпоследовательности

символов 011101.

Рисунок 4. Алгоритм выполнения

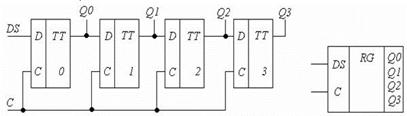

2. ВЫБОР МИКРОСХЕМЫ РЕГИСТРА СДВИГА

Кроме операции хранения данных регистры могут

использоваться и для операции сдвига данных с целью преобразования двоичного

последовательного кода в параллельный и наоборот. Это так называемые сдвиговые

регистры или регистры сдвига, которые получаются путем цепочного соединения

триггеров.

Суть сдвига состоит в том, что по сигналу

синхроимпульса происходит одновременная перезапись содержимого каждого триггера

в соседний триггер. При этом не меняется само двоичное слово (число),

записанное в регистре, оно лишь сдвигается на один разряд и только содержимое

последнего триггера ТТ3 пропадает из регистра, а на вход первого ТТ0 поступает

новый бит.

Рисунок 5. Сдвигающий регистр

Сдвигающий регистр в отличие от регистра памяти

должен обязательно состоять из непрозрачных триггеров, иначе при первом же

сигнале сдвига бит, поступивший на вход первого триггера регистра сдвига, сразу

же пройдёт на выход этого триггера и соответственно, на вход второго триггера,

а значит и на выход второго триггера и т. д. до последнего триггера регистра

сдвига.

В некоторых сдвиговых регистрах сдвиг происходит

не только в одну сторону, а и влево и вправо - это так называемые реверсивные

регистры.

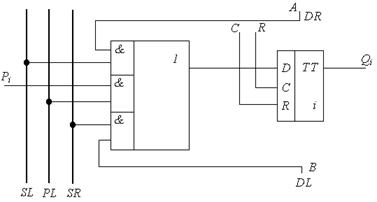

Чтобы обеспечить реверс сдвига и параллельную

запись сразу во все триггеры к D-входу каждого i-того триггера подключён

мультиплексор, который при подаче " 1 " на один из управляющих входов

- SL(Shift Left - сдвиг влево), SR(Shift Right - сдвиг вправо) или PL(Parallel

load - параллельная загрузка) подключает вход i-того триггера соответственно к

выходу младшего соседа (направление A), старшего соседа (направление B) или к

выходу параллельной загрузки Di (см. рис.2). Точка A самого младшего триггера

(разряда) является входом DR, точка В самого старшего разряда - входом DL

(входы DL и DR используются для наращивания разрядности реверсивных регистров).

Выход i-го триггера подключён к соответствующим входам мультиплексоров соседних

разрядов. По С-сигналу триггеры регистра принимают информацию с направлений,

диктуемых мультиплексорами.

Рисунок 6. Схема одного разряда реверсивного

регистра

На рисунке 6 представлена принципиальная схема

сдвигового регистра с параллельным и последовательным вводом данных.

P/S

- Parallel/Serial

- выбор режима работы

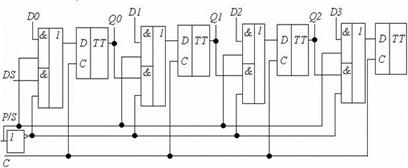

Чтобы 4-х разрядное двоичное число,

представленное в параллельном коде, преобразовать в последовательный код, надо

сначала разряды этого числа подать на входы D0,D1,D2,D3 регистра, а

одновременно с этим подать разрешение на параллельную запись, т.е. P/S = 1 и

подать один или несколько импульсов на С-вход регистра. После этого нужно

запретить параллельную запись в регистр и тем самым разрешить последовательный

режим регистра (P/S = 0). Теперь на каждый синхроимпульс выход D3 будет

выдавать поочерёдно разряды записанного двоичного числа. Обычно

последовательный код начинается младшим разрядом, а в данном регистре первым на

выход поступит разряд числа, записанный ранее на триггер ТТ3, значит при

параллельной записи следует проследить, чтобы младший разряд был записан в

триггер ТТ3, а старший - в ТТ0.

Рисунок 8. Преобразование параллельного кода в

последовательный

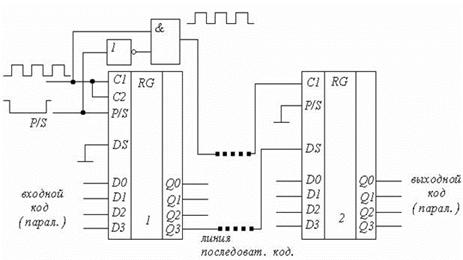

Рассмотрим схему преобразования параллельного

кода в последовательный, приведённую на рис. 8. Данные параллельным кодом

загружаются в регистр RG1, пока P/S=1. Затем при P/S=0 RG1 переходит в режим

сдвига (последовательный режим) и в течение 4-х импульсов на С- входе RG1

содержимое этого регистра с его выхода Q3 разряд за разрядом передаётся на RG2

на вход DS, где записывается последовательным кодом благодаря подаче 4-х

синхроимпульсов на вход C RD2. После этого данные могут быть считаны

параллельным кодом с выходов Q0-Q3 регистра RG2.

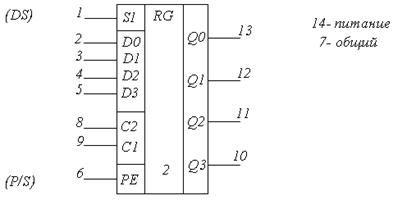

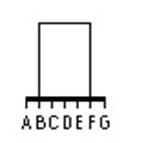

Рисунок 9. Условное обозначение и цоколевка

микросхемы К155ИР1

бинарный бесконечный микросхема

генератор

3. МЕТОДИКА ОТЛАДКИ МОДЕЛИ УСПБ

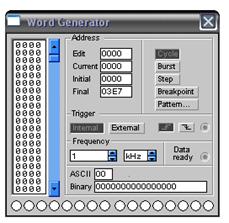

3.1 Генератор слов

Генератор слов используется для задания цифровых

последовательностей. На рисунке 10 приведено уменьшенное изображение генератора

слов.

Рисунок 10. Уменьшенное изображение генератора

слов

На шестнадцать выходов в нижней части генератора

параллельно подаются биты генерируемого слова. На выход тактового сигнала

подается последовательность тактовых импульсов с заданной частотой. Вход синхронизации

используется для подачи синхронизирующего сигнала от внешнего источника.

Двойным щелчком мыши по уменьшенному изображению

генератора слов открывается его расширенное изображение. На рисунке 11

представлено расширенное изображение генератора слов.

Рисунок 11. Расширенное изображение генератора

слов

Левая часть генератора отображает любые 16 (из

2048) шестнадцатибитовых слов, которые отображаются как четырехразрядные

шестнадцатиричные числа. Выделением отмечается слово, активное в данный момент.

Значения битов этого слова отображаются в круглых окнах внизу на панели

генератора. Ввод слов может производиться в окне «Bimary»

генератора при помощи мыши и клавиатуры. Нажатием на левую клавишу мыши

выделяется нужный бит, а ввод значения 0 или 1 производится с клавиатуры.

Ввод данных может также осуществляться путём

ввода с клавиатуры четырёх шестнадцатиричных чисел в левую часть генератора

слов, используя символы, идентичные приведенным в таблице 1. При вводе можно

пользоваться клавишами на клавиатуре ←,↑,→,↓.

Генератор может работать в трех режимах:

• пошаговый (каждый раз после подачи очередного

слова на выход генератор останавливается);

• циклический (на выход генератора однократно

последовательно поступают все 2048 слов);

• непрерывный (все 2048 слов циклически

передаются на выход генератора в течение необходимого времени).

Нажатием на кнопку STEP (рис. 11) генератор

переводится в пошаговый режим, кнопка BURST переводит в циклический режим, а

кнопка CYCLE - в непрерывный. Для того чтобы прервать работу в непрерывном

режиме, необходимо еще раз нажать кнопку CYCLE (или CTRL+ T на клавиатуре).

Используя окно «Final»

можно зацикливать последовательность из произвольного числа слов. Для этого

достаточно ввести в это окно шестнадцатиричное значение (по сути, номер)

последнего в последовательности слова.

Правая нижняя панель управления TRIGGER

определяет момент начала работы генератора. Момент запуска может быть задан по

положительному или отрицательному фронтам синхронизирующего импульса. В режиме

EXTERNAL (внешняя синхронизация) передача слов на выход генератора

синхронизируется с помощью импульсов, подаваемых на вход запуска. С приходом

каждого импульса на выход генератора выдается одно слово. В режиме INTERNAL

(внутренняя синхронизация) генератор производит внутреннюю синхронизацию

передачи слов на выход.

Для синхронизации работы схемы с генератором

можно использовать выход Clock Pulse (Clk). Установить частоту импульсов в

пределах от Гц до МГц можно в окне FREQUENSY.

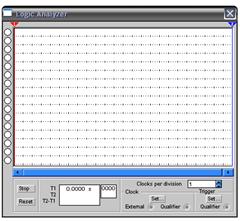

3.2 Логический анализатор

На рисунке 12 показано уменьшенное изображение

логического анализатора. Логический анализатор подключается к исследуемой схеме

с помощью выводов в его левой части. Одновременно могут наблюдаться сигналы в

шестнадцати точках схемы. Нижние клеммы используется для подачи

синхронизирующих импульсов и управления анализатором.

Рисунок 12. Уменьшенное изображение логического

анализатора

Двойным щелчком мыши по уменьшенному изображению

открывается расширенное изображение логического анализатора, приведенное ниже

на рисунке 13. Временные диаграммы сигналов на экране 16-канального логического

анализатора изображаются в виде прямоугольных импульсов. Кроме того, круглые

окна в левой части анализатора показывают текущее состояние входов анализатора.

Каждое окно соответствует одному из его входов. Уровни сигналов, в текущий

момент подающихся на вход анализатора, на экране отображаются справа. Нажатие

на клавишу CLEAR очищает экран логического анализатора. В поле CLOCKS

PER DIVISION

устанавливается временной масштаб по горизонтальной оси.

Выбор режима синхронизации производится при

помощи поля управления TRIGGER. Существует два режима синхронизации:

· внутренняя синхронизация;

· внешняя синхронизация.

Режим внешней синхронизации устанавливается

нажатием на кнопку EXTERNAL. В этом режиме синхронизация производится

синхронизирующим импульсом от внешнего источника, подаваемым на вход

синхронизации. При помощи кнопок, расположенных в поле управления, можно задать

момент запуска по положительному или отрицательному фронту синхронизирующего

импульса.

Кнопкой Set

в секции Clock

устанавливается частота фиксации значений анализируемых сигналов. При

совместной работе генератора слов и логического анализатора его частота работы должна

быть не менее чем в 10 раз выше частоты формирования слов генератором слов. Для

того, что бы можно было фиксировать логическим анализатором риски сбоя в

логических схемах его частота работы должна быть порядка 100 МГц, а частота

работы генератора слов - порядка 10 МГц.

Рисунок 13. Расширенное изображение логического

анализатора

4. ВЫБОР МИКРОСХЕМЫ ДЛЯ РЕАЛИЗАЦИИ

БЛОКА ИНДИКАЦИИ

Семисегментный светодиодный индикатор со

встроенным преобразователем шестнадцатиричного кода в семисегментный

управляется подачей четырехразрядного двоичного кода на входы A,B,C,D,

при этом вход D соответствует

младшему разряду двоичного кода, а вход A

- старшему его разряду.

Рисунок 14. Семисегментные светодиодные

индикаторы

При моделировании отдельных функциональных

частей разрабатываемого устройства селекции бинарной подпоследовательности

разрешается использовать семисегментный светодиодный индикатор со встроенным

преобразователем шестнадцатиричного кода в семисегментный. При окончании

разработки, т.е. при разработке схемы электрической принципиальной, должна быть

использована микросхема, аналогичная модели семисегментного светодиодного

индикатора с общим катодом, а преобразователь шестнадцатиричного кода в

семисегментный должен быть разработан на микросхемах малой степени интеграции

(на логических элементах).

Зуммер управляется напряжением переменного тока,

а звуковой сигнал воспроизводится при помощи встроенного в ЭВМ динамиком.

ЗАКЛЮЧЕНИЕ

В данном курсовом проекте перед нами лежала

задача построения синхронного автомата на интегральных микросхемах. Эта задача

решается очень огромным количеством способов. Мы выбрали один из наиболее

простых, взяв за основу регистр сдвига. Человечество не стоит на месте и

развивается с очень большим потенциалом. Возможно, в будущем эта задача будет

решаться за считанные минуты.

СПИСОК ЛИТЕРАТУРЫ

1.

Тюрин С.В. Практикум по теории автоматов: синтез синхронного управляющего

автомата. Учебное пособие. Воронеж: Воронеж. гос. техн. ун.-т, 2004. 84 с.

(Электронная версия).

.

Выполнение электрических схем по ЕСКД: Справочник / С.Т. Усатенко, Т.К.

Каченюк, М.В. Терехова. - М.: Изд-во стандартов, 2012. - 316 с.

.

Угрюмов Е.П. Цифровая схемотехника. - СПб.: БХВ - Петербург, 2011

.

Новожилов О.П. Основы цифровой техники / Учебное пособие. - М.: ИП РадиоСофт,

2014. - 528 с.

ПРИЛОЖЕНИЕ

Технические условия: объектом разработки

является синхронный автомат, предназначенный для выделения и обработки заданной

бинарной подпоследовательности из бесконечной последовательности бинарных

символов. Длина селектируемой подпоследовательности -13 бит со структурой

111011010110110010010. Анализируемая подпоследовательность имеет структуру

10010010 и должна непосредственно следовать за селектируемой

подпоследовательностью. Допускаются формальный и/или эвристический способы

разработки