|

ТИПMAX3082E

|

|

|

Наличие TxD

|

1

|

|

Наличие RxD

|

1

|

|

Состояние RxD

|

Р

|

|

Быстродействие, MBPS

|

0.115

|

|

Количество станций

|

256

|

|

Защита ESD

|

±15kV

|

|

Питание

|

5 V

|

|

Ток потребления, mА

|

0.375

|

В приведённой таблице приняты следующие обозначения:

В колонке "Состояние RxD": P - обозначает, что

управляющий вход приёмника переключает его либо в открытое состояние, либо

переводит его в режим энергосбережения.

"Режим": H - означает полудуплексный режим, т.е.

интерфейс RS485.

Разработка формата протокола обмена

Обмен данными разрабатываемого устройства

с внешним устройством осуществляется посредством последовательного порта RS 485

в асинхронном режиме. Количество бит равно 7 для одного канала. Скорость

передачи согласно техническому заданию на курсовой проект равна 300 кбит/с.

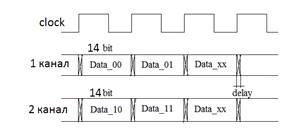

В курсовой работе мы используем два 14-разрядных

одноканальных АЦП.

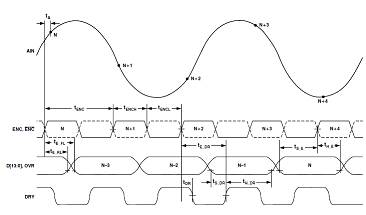

Рис. 3 - Передача данных по каналам АЦП

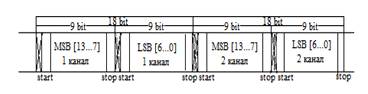

В соответствии со стандартными протоколами передача данных

через данный порт начинается со старт-бита (start bit) и заканчивается

стоп-битом (stop bit). Стартовый бит всегда равен 0 (GND), стоповый - 1 (VCC).

Послав один за другим стартовый бит, байт данных и стоповый бит, передатчик

может повторять стоп-бит до тех пор, пока приемник не будет готов получить

следующий байт. Тогда посылается стартовый бит, служащий сигналом начала новой

порции данных.

Поэтому к 14-битной посылке добавятся ещё 2 стоповых и 2

стартовых бита.

Так как элементарная посылка имеет длину 7 бит (без учёта

старт-стоп бит), а передать нужно 28 информационных бит по 14 на каждый канал,

то необходимо поделить эти 28 бит на 4 посылки по 7 бит.

Определим однозначно способ разделения посылки: пусть сначала

будут передаваться 7 старших бит (MSB) 1 канала, за ними 7 младших бит (LSB) 1

канала, затем по 7 старших (MSB) и младших (LSB) бит второго канала. Это нам

нужно для того, чтобы, принимая с АЦП данные, мы смогли "прочитать"

информацию.

Рис. 4 - Формат протокола обмена данных

Выбор ОЗУ

Мы должны выбрать ОЗУ с объёмом не менее 16 ksample на 1

канал (так как согласно заданию канала два, то нам нужно ОЗУ с объёмом памяти

не менее 32 ksample) не менее, чем на 14 бит.

Выбираем ОЗУ AS7C3513B с объёмом памяти 32K×16.

4. Анализ

временных параметров системы

При программировании ПЛИС возможны появление критических

временных соотношений, сбой и набеги сигналов. В тех случаях, когда это влияет

на правильность работы системы, были использованы задержки нужной длительности.

Также необходимо добиться, чтобы такие сигналы, как we, oe, имели длительность

не меньшую, чем указано на временных диаграммах работы ОЗУ as7c34098.

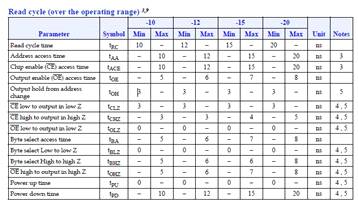

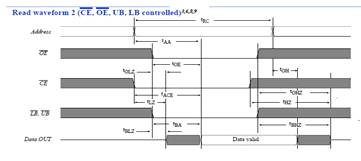

Таблица 3 - Временные параметры для режима чтения

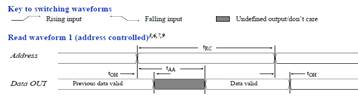

Временная диаграмма для режима чтения представлена ниже:

Рис. 5 - Временная диаграмма для режима чтения

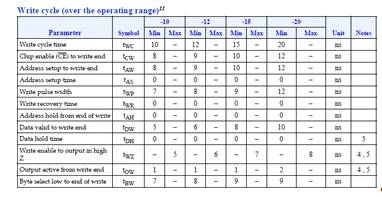

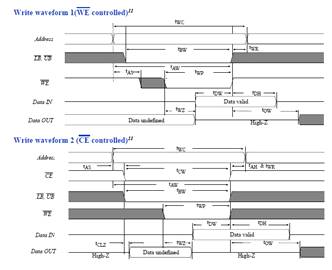

Таблица 4 - временные параметры для режима записи

Временная диаграмма для режима записи представлена ниже:

Рис. 6 - Временная диаграмма для режима записи

Так как интерфейс работает намного медленнее, чем АЦП, то

ориентироваться при выборе тактовой частоты генератора будем на последний.

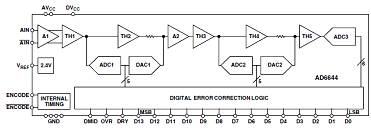

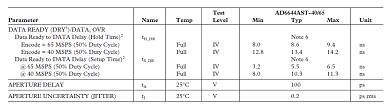

В данном разделе курсовой работы приведём функциональную

блок-схему и временную диаграмму для АЦП AD6644AST-40.

Рис. 7 - Функциональная блок-схема АЦП AD6644AST-40

Рис. 8 - Временная диаграмма для АЦП AD6644AST-40

Таблица 5

5. Разработка

файла конфигурации для системы сбора-обработки данных на языке AHDL

Для моделирования системы в среде MAX+plusII необходимо

разработать файл конфигурации на языке AHDL. В него войдут такие мега-функции,

как:

lpm_counter - счетчик, необходимый для деления

частоты, счета номеров адресов и для формирования сигнала переполнения адреса в

памяти.

lpm_compare - для сравнения цифровых данных,

поступающих от АЦП, с порогом.

lpm_bustri - для моделирования двунаправленной

шины данных.

lpm_shiftreg - для преобразования параллельного кода в

последовательный.

busmux - для реализации функции мультиплексора, для

передачи данных на выход интерфейса.

lpm_counter - счетчик, необходимый для деления

частоты, счета номеров адресов и для формирования сигнала переполнения адреса в

памяти.

lpm_compare - для сравнения цифровых данных,

поступающих от АЦП, с порогом.

lpm_ram_dq - для моделирования внутренней памяти

ПЛИС.

lpm_shiftreg - для преобразования параллельного кода в

последовательный.

busmux - для реализации функции мультиплексора, для

передачи данных на выход интерфейса.

Также использованы примитивы триггеров, таких как DFF, TFF.

Найдет свое применение неудаляемый буфер LCELL, для формирования нужных

задержек, для синхронизации в появлении сигналов записи/чтения и сигнала на

шине адреса. В секции Variable будут прописаны сигналы, которые используются

только ПЛИС, в виде внутренних узлов (node). В секции Variable будут

использованы узлы с тремя видами состояний (tri_state_node) для моделирования шины,

по которой будут считываться данные из ОЗУ в ПЛИС.

Текст программы для ПЛИС содержится в приложении 1

Программа упакована после компиляции в микросхему семейства

ACEXK50 TQFP144.

6.

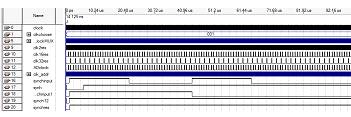

Моделирование цифровой части системы

Данная система в процессе своей работы попеременно выполняет

циклы записи и чтения в память. Цикл записи начинается после прихода в ПЛИС от

АЦП 28-разрядной кодовой комбинации (считаем, что в ПЛИС приходит объединённый

сигнал с двух каналов).

При передаче на интерфейс же возможен выбор нужного канала.

Была реализована синхронизация для двух случаев: внешняя+ и

внутренняя+, - как указано в задании, и при помощи логического "ИЛИ"

выбран тот вариант, где синхронизация сработала быстрее. D-триггером

зафиксирован выбранный вариант.

Заключение

В результате работы мы разработали систему сбора и обработки

информации на языке AHDL. Разбили структурную схему на блоки и промоделировали.

Список

литературы

1.

Техническая документация Altera.

.

Техническая документация Analog Devices.

.

Техническая документация Texas Instruments.

.

Конспект лекций по курсу "Основы построения микропроцессорных

систем".

.

Описание языка AHDL в электронном виде.

Приложение 1

Текст файла конфигурации"lpm_counter.

inc";"mux. inc";"lpm_ram_dq. inc";"lpm_mux.

inc";"lpm_shiftreg. inc";"lpm_compare.

inc";"lpm_add_sub. inc";"lpm_bustri";MODEL

(: input; - -входная тактовая частота 16МГц

делитель частоты[2.0]: input;res,clk16res,clk32res,ADclockMUX

[2.0],ADclock: output;

ОЗУ_addr [1.0],cout_addr,address_ram [4.0],ram_full,clk_address,WR:

output;: output;

синхронизация внутренняя_in [27.0], compare [27.0]: input;:

output;

Вход синхронизации внешняя: input;,synch12, synchres: output;

BUSTRI[27.0]: bidir;

Управляющие сигналы ОЗУ,OE,WE,WEres: output;

),clk16,clk32,ADread: node; - -деление частоты на 2,16,32

Первый шаг - реализация делителя частоты. Коэффициенты

деления

определяем из условий задания. Входную частоту clock

принимаем

равной выходной частоте АЦП - 40 МГц=lpm_counter (.

clock=clock) with (lpm_width=2, lpm_modulus=3)(. cout);res=dff (clk2,! clock,

vcc, vcc);=lpm_counter (. clock=clock) with (lpm_width=5, lpm_modulus=17)(.

cout);res=dff (clk16,! clock, vcc, vcc);=lpm_counter (. clock=clock) with

(lpm_width=6, lpm_modulus=33)(. cout);res=dff (clk32,! clock, vcc, vcc);[2.0] =

(clk32res,clk16res,clk2res);= mux (. data [] =ADclockMUX [],. sel [] =clkchoose

[]) with (width=3, widths=3)(. result);

Второй шаг - реализация ОЗУ. На входе модуля ОЗУ присутсвуют

2 шины

шина адреса и шина данных. ША определяет режим работы модуля

- запись или

чтение. По ШД поступают данные.

ШИНА АДРЕСА= lpm_counter (. clock=clock) with (lpm_width=2,

lpm_modulus=2)(. cout);_addr [1.0] = (ADread, ADclock);_address=mux (. data []

=clk_addr [],. sel=WR) with (width=2, widths=1)(. result);

sinh внутренняя=lpm_compare (. dataa [] =ram_in [],. datab []

=compare [])(lpm_width=28) returns (. ageb);

синхронизация внешняя + - -= tff (vcc,synchinput,vcc,vcc);=

synh or synchinput1;= dff (synch12,synch12,vcc,vcc);

------------------------------= tff (vcc,WR,lcell (! (! (!

counterclearinp))),vcc);_ram [] =lpm_counter (. clock=clk_address,. cnt_en =

synchres,. aclr = counterclearinp)(lpm_width=5, lpm_modulus=17)(. q []);

Сигнал переполнения_addr = lpm_counter (. clock=clk_address,.

cnt_en = synchres) with (lpm_width=5, lpm_modulus=17)(. cout);_full=dff

(cout_addr,! clk_address, vcc, vcc);

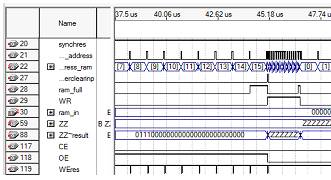

Данные направляются из АЦП в ОЗУ, а с ОЗУ на интерфейс при

переполнении ОЗУ. За это отвечает bustri

Lmp_bustri ZZZZZ это значение которые считываются с ОЗУ, так

как программно мы их не задаем,

то в симуляторе не можем их видеть[] =lpm_bustri (. data []

=ram_in [],. enabledt=! WR)(LPM_WIDTH=28) RETURNS (. tridata []);

Управляющие сигналы ОЗУ= b"0";=! tff

(vcc,WR,vcc,vcc);= dff (vcc,! clk_address,lcell (! (! (! (! (! WE and

OE))))),vcc);=! WE;;

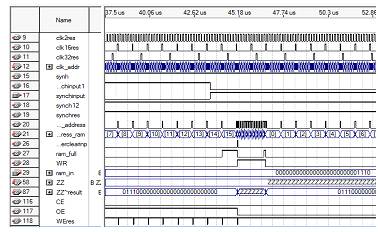

Рис. 1 - Выбор частоты и синхронизация

Рис. 2 - Счётчик адреса и управляющие сигналы ОЗУ

Рис. 3 - Общий вид

Текст файла - конфигурации, описывающий работу

интерфейса RS485"lpm_shiftreg";"lpm_mux";"busmux";"lpm_counter";"mux.

inc";RS485

( _out [13.0],clock, sel: input;[8.0],data2 [8.0],data

[17.0],clkRS485,clkread,clkRS485res,out,load1, out2, outrez, MUXout [1.0]:

output; _out2 [13.0]: input; [8.0],data22 [8.0],data2rez [17.0]: output;

),clkposled: node;= lpm_counter (. clock=clock) with

(lpm_width=8, lpm_modulus=134)(. cout);res = dff

(clkRS485,clock,vcc,vcc);=lpm_counter (. clock=clkRS485res) with (lpm_width=5,

lpm_modulus=19)(. cout);= (gnd,ram_out [6.0],vcc);= (gnd,ram_out

[13.7],vcc);[8.0] = data1 [8.0];[17.9] = data2 [8.0];= clkread;= (gnd,ram_out2

[6.0],vcc);= (gnd,ram_out2 [13.7],vcc);rez [8.0] = data12 [8.0];rez [17.9] =

data22 [8.0];= lpm_shiftreg (. data [] =data [],. clock=clkRS485res,. load =

load1)(lpm_width=18) returns (. shiftout);= lpm_shiftreg (. data [] =data2rez

[],. clock=clkRS485res,. load = load1)(lpm_width=18) returns (. shiftout);[1.0]

= (out,out2);= mux (. data [] =MUXout [],. sel [] =sel) with (width=2,

widths=1)(. result);;

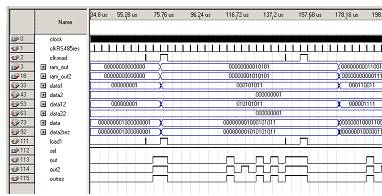

Рис. 4 - Описание работы приемника интерфейса RS485