Цифровые устройства и микропроцессоры

Министерство образования Российской

Федерации

Таганрогский государственный

радиотехнический университет

Кафедра РПрУ и ТВ

Пояснительная записка к курсовой

работе по курсу:

Цифровая обработка сигналов

Выполнил: Машлятин А.В.

студент группы РЗ-50

Проверил: Литюк В.И.

д.т.н. проф. каф. РПрУ и ТВ

Таганрог 2006 г.

Содержание

Введение

. Анализ

технического задания

. Структурная

схема АС БПФ

. Весовая

обработка данных

. Разработка

принципиальной схемы основного узла АС БПФ

Список

литературы

Введение

Современный этап развития вычислительной техники характеризуется

разработкой микропроцессорных средств. Микропроцессоры (МП) используются в

качестве элементной базы для реализации устройств обработки данных. При этом

каждая сфера применения МП предъявляет свои специфические требования к их

составу и структуре. Особенно ярко эти требования выражены в области цифровой

обработки сигналов (ЦОС), методы и средства которой широко используют в

настоящее время в различных областях народного хозяйства, науки и техники от

радио- и гидролокации до бытовой аппаратуры [5].

Как правило, задачи ЦОС требуют выполнения больших объемов вычислений над

большими массивами данных в реальном масштабе времени. При этом важность таких

задач делает целесообразной разработку специализированных устройств для их

решения. До недавнего времени такие спецпроцессоры выполнялись на

микроэлектронной базе общего назначения, в результате чего эффективность их

применения была низкой.

Возрастание требований к технико-экономическим показателем современных

систем ЦОС, расширение областей применения и усиливающая тенденция к

параллельным (конвейерным) методам их организации, привели к созданию

специализированных комплектов БИС для построения систем ЦОС: К1802; К1804, а

также комплект К1815, на базе которого наиболее выгодно построить цифровую

систему обработки информаций [4].

1. Анализ технического задания

Важной разновидностью ЦОС является цифровые анализаторы спектра разных

видов. Можно отметить, что спектральный анализ находит применение в задачах,

обнаружения (т.е. когда принимается решение о наличие или отсутствии сигнала на

какой-либо частоте), задачи классификации типа сигнала (т.е. определяют

источник сигнала и его характеристики), а также решают задачи определения и

локации местонахождения источника сигнала (т.е. находят дальность и пеленг)

[3].

При этом наиболее важными характеристиками спектрального анализа являются

[2,3]:

количество частот, на которой желательно измерить спектр;

разрешающая способность измерителя спектра.

Цифровой спектральный анализ может осуществляются как в режиме «скачущее»

окно, так и в режиме «скользящее» окно. Техническая реализация может быть

осуществлена при помощи устройств, выполняющих либо параллельный спектральный

анализ, либо последовательный. В первом случае требуются существенные затраты

оборудования, а в другом - необходимо выполнить условия эргодичности и

стационарности анализируемых случайных процессов.

Спектральный анализ, осуществляемый в режиме «скачущие» окно (задано по

Т3), основывается по алгоритму быстрого преобразования Фурье (БПФ), т.к. задача

изменения спектра сводится к похождению значений Z - преобразования конечной реализации сигнала для большого

числа точек, равномерно распределенных по окружности единичного радиуса [3]. То

алгоритм БПФ может быть реализован либо программным путем на универсальной

цифровой вычислительной машине (ЦВМ), либо путем построения специализированного

вычислителя.

Применение ЦВМ не оправдано экономически, из-за своей «универсальности»,

они имеют сравнительно высокую цену и при этом, как правило, не слишком высокую

производительность [2].

Поэтому для реализации нашего анализатора спектра на основе алгоритма БПФ

(АС БПФ) можно выбрать микропроцессорные наборы БИС различных серий [6].

Поэтому представляет интерес сравнения этих наборов по обобщенному критерию

качества который включает производительность П, числа корпусов для выполнения

выбранного типа операций К, число вывода каждого корпуса В и потребляющую одним

корпусом мощности Р.[5]:

(1);

(1);

Данный обобщенный критерий качества независимо от вида сравниваемых

устройств обработки, реализующих рассматриваемых устройств обработки,

реализующих рассматривания алгоритма ЦОС, позволяет оценить эффективность

применяемых микросхем. Знак суммы в знаменателе выражения (1) характеризует

конструктивную не однотипность используемых в какой-либо серии микросхем.

Используя это выражение, приведем результаты сравнительного анализа

вариантов реализации операций БПФ на микросхемах серии К1802 [6], и микросхемах

К1815ВФ3 [4], специально разработанных для реализации алгоритма.

Рис 1. Графики сравнительного анализа эффективности

микросхем серий К1802 и К1815

Остановимся на особенностях реализации систем ЦОС на основе элементарной

цифровой комплексной ячейки (ЦКЯ). Основным алгоритмом при линейной обработке

сигнала является решение системы уравнений, которая в матричной форме записи

имеет вид [2]:

(2)

(2)

где X - вектор столбец входных данных,

представляющих собой либо комплексные величины, либо квадратурных составляющие;

Y -

вектор столбец выходных данных в виде комплексных величин либо квадратурных

составляющих;

W -

матрица комплексных составляющих весовых коэффициентов (или квадратных

составляющих).

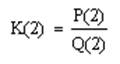

Из (2) видно, что задача обработки сигналов в общем случае сводится к

повороту и изменению масштаба в многомерном масштабе пространства вектора

входных данных. Очевидно, что матрица W комплексных весовых коэффициентов может быть технически реализована

различными способами, а ее элементами являются коэффициенты передаточной

функции цифрового фильтра, описываемого в виде отношения номиналов требуемых

порядков на Z- плоскости [4]:

(3)

(3)

Передаточная функция (3) может быть представлена либо в виде произведения

отношений номиналов первого порядка, либо в виде их суммы произведений. В

зависимости от вида записи выражения (3) различают последовательное,

параллельное, параллельно-последовательное соединение элементарных звеньев

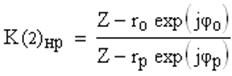

(ЦКЯ), передаточная функция каждого из которых по Z-плоскости записывается в виде:

(4)

(4)

где r0 - модуль и фазовый сдвиг простейшего пере курсивного

фильтра (фильтра с конечной импульсной характеристикой - КИХ-фильтра);

rp и p - модуль и фазовый сдвиг полюса

простейшего рекурсивного фильтра (с бесконечной импульсной характеристикой -

БИХ-фильтра) [4,9].

Структурная схема элементарной ЦКЯ, реализующей выражение (4), на основе

которой может быть получена передаточная функция (3), записанная в любом из

указанных видов, изображена на рис. 2,а; где двойные стрелки показывают, что

передаются коды комплексных чисел.

Данная элементарная ЦКЯ представляет собой:

- при rp=0,4; =0; r0=1 - цифровой дифференциатор, простейший КИХ - фильтр;

при rp=1; p=0; r0=0 - цифровой интегратор, простейший

БИХ - фильтр;

при rp=0; 0; r0=1 - цифровой эквивалент аналогового последовательного

контура;

при rp<1; p = 0; r0

= 0 - цифровой

эквивалент аналогового последовательного контура, цифровой резонатор;

при rp=1; r0=0; p =

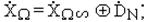

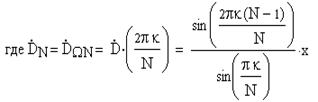

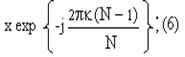

2nk/N - данная цифровая ЦКЯ производит вычисление точного значения

коэффициента ДПФ согласно выражения:

(5)

(5)

где N- число комплексных отчетов входной

реализации 0kM - 1; T - период дискретизации (из теоремы Котельникова).

Рис.

2, а Структурная схема ЦКЯ с прямыми и обратными связями.

Рис.

2, б Структурная схема ЦКЯ алгоритма БПФ

В случае, когда известны начало и конец входной реализации, широкое

применение находит различного вида алгоритмы быстрого расчета ДПФ - алгоритмы

БПФ.

Структурная схема реализации базовой операции БПФ представлена на рис. 2,

б [4].

При проведении спектрального анализа отклик в частной области при

воздействии на входе отрезка дискретной синусоиды, состоящей из N - отчетов, будет иметь вид sin x/x, это приводит к

тому, что спектр отрезан дискретной синусоид как бы «растекается» по оси

частот, что является вредным эффектом при проведении спектрального анализа. Это

эффект особенно опасен в тех случаях, когда в анализируемом отрезке реализации

присутствуют несколько частот, амплитуд которых существенно отличаются между

собой. При этом возможна, «маскировка» тех спектральных составляющих,

интенсивности которых малые, а их частоты расположены в пределах боковых

лепестков спектральной составляющей [3, 5].

Для устранения указного эффекта находят применение различного вида

«временные окна». Под «временным окном» понимают модулирующую функцию, на

которую умножается отрезок входной реализации, наступающей на обработку [2, 3,

4, 5].

Существует достаточно большой диапазон окон, обладающих достаточно

высоким подавлением уровня боковых лепестков (до 50дБ [3]), но в тоже время,

«цена» высокого уровня подавления выражается в соответствующем ухудшении

разрешающей способности, отсчитываемой на заранее обусловленном уровне.

По рекомендации из [2, 3, 4, 7] применим в АС БПФ весовое окно Ханна [3] для

заданного Т3 N=8.

.

Структурная схема АС БПФ

Анализ архитектур разработанных в настоящее время МП и использование ими

набора операций показывает, что непосредственное применение их в

многопроцессорных системах ЦОС вызывает определенные затруднения. Можно

сформулировать требования, которые должны удовлетворять МП, используемый в

современных многопроцессорных системах ЦОС. К таким требованиям можно отнести

[4,9].

- использование стандартного корпуса с минимально возможным числом

выводов при условии обеспечения минимальной потребляемой мощности и

максимальной степени интеграции БИС;

- реализация макроопераций и использование языка высокого уровня

путем одновременного выполнения всех арифметическо-логических действий в

многопроцессорной системе за счет соединения определенным образом отдельных МП

по коду крупной операции;

применение принципа параллельности выполнения всех обменов и

арифметическо-логических действий, входящих в реализуемые МП крупные операции;

применение конвейерной обработки информации при высокой тактовой

частоте работы МП.

Цифровая часть структурной схемы классической доплеровской

Радиолокационной системы с АС БПФ приведена на рис.3 [4,5].

Работает система следующим образом. С выхода линейной части РЛС РПрУ

аналоговый сигнал поступает на квадратурный смеситель КвСм, формирующий на

выход квадратурные составляющие входного сигнала S(t): Re=S (t)cost и Im=S(t)sinT. Квадратурные составляющие поступают

на аналого-цифровой преобразователь АЦП, формирующий из них цифровые потоки в

параллельном коде. С выхода АЦП отрезки реализации поступают поочередно через

коммутатор Ком.1 на ортогональную регистровую память ОРП, выполненную на

микросхемах К1815ИР1, где преобразуются из параллельного кода в

последовательный знакоразрядный код. Преобразованные коды параллельно

оперативное запоминающее устройство ОЗУ, через коммутатор Ком.2 и перемножитель

Перем, формирующий отчеты с учетом весового окна, поступают на блок БПФ,

выполненный на МП К1815ВФ3. Достоинством алгоритма БПФ является использование

одного ОЗУ как для входных частотных отчетов, которые через тот же коммутатор

Ком.2 поступают на ОРП, выполняющие обратное преобразование из

последовательного знакоразрядного кода в параллельный код, который через

объединитель потока ОБП, поступает на исполнительное устройство ИУ и на управляющую

ЦВМ доплеровской РЛС. Управляющая ЦВМ формирует тактовые сигналы с частотой

дискредитации для работы

цифровой анализатор информация микропроцессор

АЦП-Тд, коэффициенты весового окна для работы перемножителя W(t) и сигналы управления для квадратурного гетеродина,

формирующего сигналы опорной частоты для получения квадратурных составляющих

входного сигнала.

Найдем необходимое число разрядов АЦП. По заданному в Т3 диапазону

входных сигналов Dbx=48

дБ. Учитывая тот факт, что минимальный уровень входного сигнала не задан,

похожим что минимальное отношение сигнала/шум равно единице, а следовательно,

количество разрядов АЦП будет равно

Rацп=Dbx/6=48/6=8 разрядов

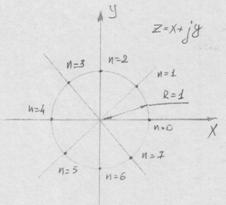

Найдем положение нулей и полюсов на Z-плоскости АС БПФ. Из (4) с учетом rp=1; r0=0; p=2nk/N, получим [7]:

- т.е. полюса АС БПФ расположены на единичной окружности в точках

пересечения этой окружности с лучами углов p=2nk/N; где n=0,…,…N-1.

Для N=8 имеем таблицу 1 и рис. 4.

Таблица 1

|

№

|

U

|

rp

|

p

|

|

1

|

U1

|

1

|

20/8=0

|

|

2

|

U2

|

1

|

21/8=1/4

|

|

3

|

U3

|

1

|

22/8=1/2

|

|

4

|

U4

|

1

|

23/8=3/4

|

|

5

|

U5

|

1

|

24/8=

|

|

6

|

U6

|

1

|

25/8=5/4

|

|

7

|

U7

|

1

|

26/8=3/2

|

|

8

|

U8

|

1

|

27/8=7/4

|

Рис. 4. Положение полюсов на Z-плоскости

3. Весовая обработка данных

Разрешающая способность является характеристикой специального анализа и

зависит от числа обрабатываемых отчетов N. При этом имеющуюся запись данных конечной длительности

удобно рассматривать как некоторую часть соответствующей бесконечной

последовательности, видимую через применяемое весовое окно [3,4,5,]. При этом,

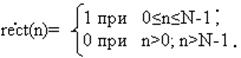

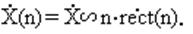

последовательность наблюдаемых данных X(n) из N отчетов можно представить как произведение прямоугольной

функции единичной амплитуды:

и бесконечной последовательности;  т.е.:

т.е.:

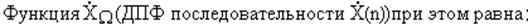

При этом допустим, что все ненаблюдаемые отсчеты равны нулю.

Т.о. Полоса пропускания АС БПФ в основном определяется весовой обработкой

входного сигнала и выбором соответствующих коэффициентов в блоке пере множителя

(рис 3). По рекомендации из [4] для N≤64 применим окно Ханна со следующей дискретно - временной функцией

[3]:

K(nТ) = 0,5+0,5cos2πn; n=0… N-1. (7);

Тогда

частотная характеристика АС БПФ будет иметь вид

Согласно (6) получим:

4. Разработка принципиальной схемы основного узла АС БПФ

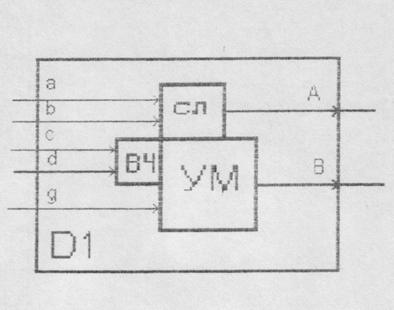

Для основного узла доплеровской РЛСАС БПФ применим основной

микропроцессор К1815ВФ3. Структурная схема этого МП приведена на рис 7. Эта

микросхема выполняет унифицированную совокупность операций, на основе которой

может быть построена каждая из крупных операций ЦОС. На рис 7: Сл - блок

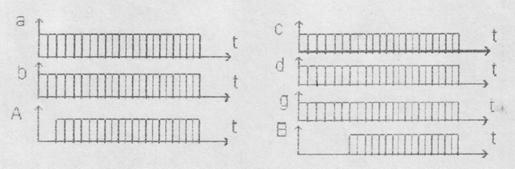

операций сложения; Вч - блок операций вычитания; Ум - блок операций умножения; a, b, c, d, g - входы; А и В - выходы.

При использовании данного МП для построения процессоров БПФ, необходимо

учесть следующее. Выходная информация получается в результате выполнения

различных операций (см. рис. 7), так, А = ab; B = (cd)g - это приводит к тому, что если операнды на выход МП

поступают синхронно, то результаты на выходе будут появляться асинхронно, как

это представлено на обобщенной временной диаграмме рис 8. - т.е. число Ф имеет

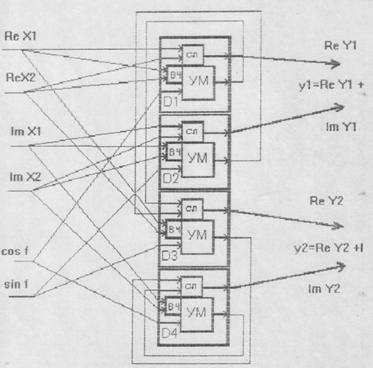

один масштаб, а В - другой. На рис 9 представлена структурная схема реализации

операции БПФ на МП К1815ВФ3. Для реализации БПФ на данной схеме числа на выходе

МП должны быть в одном масштабе. Если упрощенно принять, что сумматор и

множительное устройство имеют одинаковую задержку, равную D, то с учетом вышеизложенного, МП

должен выполнять следующие операции:

1. A = D(ab)B = 2D(cd)g

. A = 3D(ab)B = 2D(cd)g

Здесь символы D; 2D; 3D перед операцией означают, что результат данной операции

базируется с задержкой на D, 2D и 3D таков соответственно по отношению к поступающим операндам.

Для этого в блок суммирования вводят управляемую задержку,

настраивающуюся с помощью кодов операций. Краткая техническая характеристика

БИС и назначение выводов приведены в приложении 3 [4].

Рассмотрим структурную схему реализации БПФ на МП К1815ВФ3 - рис. 9. Из

нее видно, что для получения базовой бабочки БПФ требуется 4 МП. Т.о. при N = 8 получим:

МП = N/2/24 = 16 микросхема.

В приложении 4 приведена схема электрическая принципиальная одного из

блоков АС БПФ, выполненного на 4-х процессорах К1815 ВФ3, выполняющего базовую

«бабочку» БПФ для двух чисел. Для реализации 8-точечного БПФ (N=8) потребуется 4-ре таких блока [4].

Т.о. для заданного N = 8

потребуется:

- МП К1815ВФ3 - 16 шт;

- Резисторов питания-16 шт;

Разъемов 4pin;

Мощность источника питания: 300мА А

Рис. 7. Структурная схема БИС К1815ВФ3

Рис. 8. Временные диаграммы БИС К1815ВФ3

Рис. 9. Структурная схема алгоритма БПФ на К1815ВФ

Список литературы

1. Методическое

руководство к курсовому проекту по курсу «Методы и устройства цифровой

обработки сигналов в радиоприемных устройствах». Таганрог ТРТИ 1994 г. МУ№2086

2. В.И.

Лютик. Автоматизированное проектирование цифровых фильтров на базе

микропроцессорной техники. Учебное пособие Таганрог: ТРТИ 1987 г. №1339.

. В.И.

Лютик. Методы расчета и проектирования цифровых многопроцессорных устройств

обработки сигналов. Часть 1 Таганрог ТРТИ 1994 г. МУ№2231-А.

. Под

ред. Сухопарова А.И. Микропроцессорный комплект БИС серии К1815 для цифровой

обработки сигналов М: Радио и связь 1992 г.

. Цифровые

фильтры и устройства обработки сигналов на интегральных микросхемах. Под ред.

Высоцкого Б.Ф. М: Радио и связь 1984 г.

. Справочник:

Микропроцессоры и микропроцессорные комплекты интегральных микросхем: Том 1.

Под ред. В.А. Шахова. М: Радио и связь 1988 г.

. Г.

Корп, Т. Корп. Справочник по математике для научных работников и инженеров

«Наука» Главная редакция физ-мат литературы. Москва 1968 г.

. Цифровые

фильтры в электросвязи и радиотехнике. Под ред. Л.М Гольденберга