Проектування спеціалізованого мікрокомп’ютера з неоптимізованою системою команд

КУРСОВА

РОБОТА

з

дисципліни

Цифрові

ЕОМ

Проектування

спеціалізованого мікрокомп’ютера з не оптимізованою системою команд

Технічне

завдання

1. Спроектувати

спеціалізований мікрокомп’ютер

з не оптимізованою системою команд.

. Вихідні дані:

) область призначення -

рішення науково-технічної задачі F=Sh(Z1*Z2);

) елементна база - МПК

КМ1804 (ВУ4, ВС1, ВР1), КР1533;

) адресний простір пам’яті

АП=64

Кслів;

) ємність ОЗП NRAM=48Кслів,

ІМС К132РУ10;

) ємність ПЗП NROM=16Кслів,

ІМС КМ555PE4;

) кількість ПВВ NПВВ=32;

) адресність команд АК=3;

) адреса першої команди

програми 100h;

) довжина машинного слова n=24;

) команди та дані мають однакову

довжину, що дорівнює довжині машинного слова;

) для адресації ПВВ використовується

адресний простір пам’яті;

) за ІМС малої та середньої

інтеграції використовується серія КР1533.

. Креслення:

) Схема алгоритму рішення

задачі.

) Схема алгоритму

функціонування мікрокомп’ютера.

) Структурна схема мікрокомп’ютера.

) Формат мікрокоманди.

) Принципова схема мікрокомп’ютера.

ЗМІСТ

Вступ

.

Система команд мікрокомп’ютера

.1

Схема алгоритму рішення задачі

.2

Програма задачі в змістовній формі

.

Розподіл адресного простору пам’яті

.

Визначення формату команди

.1

Довжина поля КОП

.2

Кодування машинних операцій

.3

Вибір режиму адресації

.3.1

Пряма адресація

.3.2

Опесердковано-регістрова адресація

.

Формати команд і алгоритм функціонування мікрокомп’ютера

.1

Формати і цикли команд

.2

Схема алгоритму функціонування мікрокомп’ютера

.

Програмно-мікропрограмна модель мікрокомп’ютера

.

Мікропрограми операцій

.1

Арифметичні операції

.1.1

Операція «Додавання»

.1.2

Операції «Множення» і «Ділення»

.1.3

Операція «Множення»

.1.4

Операція «Ділення»

.1.5

Операція умовного переходу JNZ

.1.6

Такт збереження ТО3

.2

Мікропрограми тактів Твк, ТО1, ТО2

.2.1

Такт вибірки команди Твк

.2.2

Такти вибірки операндів То1, То2

.2.3

Мікропрограма IPL

.3

Такт декодування коду операції Тд

.4

Розподіл адресного простору пам’яті мікрокоманд

.

Структурна схема мікрокомп’ютера

.1

Процесор

.1.1

Блок мікропрограмного керування

.1.2

Блок регістрів

.1.3

Блок обробки даних БОД

.2

Пам’ять

.2.1

Оперативна пам’ять

.2.2

Постійна пам’ять

.2.3

Дешифратор ПВВ

.2.3

Дешифратор DC АП

.3

Генератор тактових імпульсів (ГТІ)

.

Формат мікрокоманди.

.

Закодована мікропрограма мікрокомп’ютера

Висновки

Список

використаних джерел

Вступ

Завданням даного курсового проекту

було спроектувати спеціалізований мікрокомп’ютер.

Процес проектування буде розділений

на два етапи: архітектурний та технічний. На архітектурному етапі буде розроблений

алгоритм рішення задачі, визначена система команд, розроблений алгоритм

функціонування мікрокомп’ютера, розроблені мікропрограми арифметичних, логічних

операцій та основних тактів, розроблена структура мікрокомп’ютера, а також

вибрані оптимальні мікросхеми для їх реалізації. Результатом технічного етапу

буде принципова схема.

.

1. Система команд мікрокомп’ютера

.1 Схема

алгоритму рішення задачі

Задача F=Sh(Z1*Z2)

відноситься

до класу науково-технічних. Для обчислення функції Sh

використовується степеневий ряд:

Схема алгоритму рішення

задачі наведена нижче і деталізована до арифметичних операцій (операторів

присвоювання). Зі схеми випливає такий набір арифметичних операцій: { + , * , /

}.

1.2

Програма задачі в змістовній формі

Програма задачі наведена в табл. 1.

З неї випливає система операцій мікрокомп’ютера:

{ + , * , / , JNZ

, HLT}.

Отже, загальне число машинних

операцій М=5.

Таблиця 1

|

№

|

КОП

|

А1

|

А2

|

A3

|

|

1

|

*

|

Z1

|

Z2

|

R1

|

|

2

|

*

|

R1

|

R1

|

R1

|

|

3

|

+

|

k

|

k

|

R2

|

|

4

|

+

|

R2

|

<1>

|

R3

|

|

5

|

*

|

R2

|

R2

|

R3

|

|

6

|

/

|

R1

|

R3

|

R3

|

|

7

|

*

|

R3

|

Uk-1

|

Uk

|

|

8

|

+

|

Uk

|

<0>

|

Uk-1

|

|

9

|

+

|

∑Uk

|

Uk

|

∑Uk

|

|

10

|

+

|

k

|

<1>

|

k

|

|

11

|

JNZ

|

3

|

-

|

-

|

|

12

|

+

|

U0

|

∑Uk

|

F

|

|

13

|

HLT

|

-

|

-

|

-

|

. Розподіл адресного простору пам’яті

Адресний простір пам’яті АП=64Ксл

розподіляться для розміщення підмножин адрес RAM,

ROM та ПВВ.

Підмножина адрес RAM

NRAM=48Kсл,

nA

RAM=]log248K[=16;

число шістнадцяткових цифр в адресі дорівнює 16/4 = 4.

Діапазон адрес RAM

(0000h

- BFFFh).

Підмножина адрес ROM

NROM=4Ксл,

nA

ROM=]log24K[=12;

число шістнадцяткових цифр в адресі дорівнює 12/4 = 3.

Діапазон адрес RОM

(000h

- FFFh).

Підмножина адрес ПВВ

NПВВ=32,

nA

ROM=]log232[=5

Діапазон адрес ПВВ (00h

- 1Fh).

Адресний простір АП=64Ксл.

Необхідна розрядність адреси:

nA

АП=]log264K[=16;

число шістнадцяткових цифр в адресі дорівнює

6/4 = 4.

Діапазон адрес АП (0000h

- FFFFh).

Можливий розподіл АП пам’яті

показаний на рис. 1. Максимальне значення адрес пам’яті:

Amax=D01Fh.

Цьому значенню відповідає довжина двійкової фізичної адреси коду n=16.

Таким чином, адресна шина мікрокомп’ютера має 16 ліній.

Рис. 1

Такому розподілу АП пам’яті

відповідає структурна схема вибору RAM,

ROM, ПВВ, що зображена

на рисунку 2.

Рис. 2

.

Визначення формату команди

Відповідно до технічного завдання

команда має структуру:

3.1

Довжина поля КОП

Мінімальна довжина поля КОП

визначається за формулою:

nКОП=]log2(M+1)[=]log2(5+1)[=3

3.2

Кодування машинних операцій

Ніяких обмежень на коди операцій в

полі КОП немає, тому використовуємо довільні значення кодів.

Коди машинних операцій подано в

табл.2.

Таблиця 2

|

КОП(15:13)

|

Операція

|

|

000

|

NOP - нема

операції

|

|

001

|

+ - додавання

|

|

010

|

* - множення

|

|

011

|

/ - ділення

|

|

100

|

JNZ - умовний

перехід

|

|

101

|

HLT - зупинка

|

3.3 Вибір

режиму адресації

.3.1 Пряма

адресація

Коди адрес А1(А2,A3)

є фізичними. Довжина адресного поля А1(А2,A3)

визначається за формулою:

A1(A2,A3)=(n-nКОП)/3=(24-3)/3=7.

Через те, що nA1(A2,A3)=7<nФА=16,

використання прямої адресації неможливе.

3.3.2

Опесердковано-регістрова адресація

У цьому випадку команда має

структуру:

де ПА1(ПА2,ПА3)

- однака режиму адресації

- регістрова

ПА1(ПА2,ПА3) =

- опосередкована

R1(R2,R3)

- адреси РЗП.

Нехай кількість РЗП NРЗП=8.

Тоді довжина поля R1(R2)

буде

Ri=]log2NРЗП[=]log28[=3.

Перевіримо виконання умови

КОП+3*nПАі+3*nRi=3+3+9=15<n=24.

Використання

опосередковано-регістрової адресації можливе.

Формат команди мікрокомп’ютера

буде:

.

Формати команд і алгоритм функціонування

мікрокомп’ютера

4.1

Формати і цикли команд

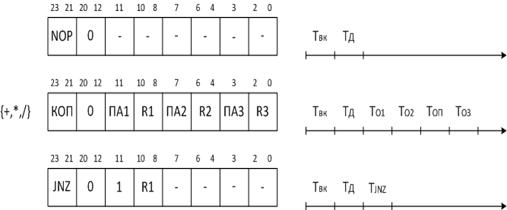

На рис.3 наведені формати і цикли

команд мікрокомп’ютера.

Перші два

такти Твк та Тд

є спільними для усіх команд і реалізують вибірку команд з пам’яті та їх

декодування. Такти ТО1 та ТО2 забезпечують вибірку

операндів на мікрокомандні регістри внутрішньої пам’яті

мікокомп’ютера.

Рис.3

.2 Схема

алгоритму функціонування мікрокомп’ютера

Схема алгоритму являє собою

сукупність мікропідпрограм (МПП):

- IPL

- пуск мікрокомп’ютера

та завантаження початкової адреси в програмний лічильник;

Твк - вибірка

команди з пам’яті;

ТО1, ТО2

- вибірки першого та другого операндів;

(+,*,/) - відповідні

арифметичні операції;

- TO3 - запис

результату;

- JNZ - операція

умовного переходу;

- HLT

- зупинка мікрокомп’ютера.

Переключальній вершині КОП

відповідає такт декодування коду операції.

.

Програмно-мікропрограмна модель мікрокомп’ютера

Модель мікрокомп’ютера

базується на використанні ВІС КМ1804ВС1, що

має

регістрову пам’ять ємністю в 16

слів.

У програмній моделі відображені

регістри, які представляються в командах мікрокомп’ютера;

в мікропрограмній моделі - регістри, вмістом яких оперують мікрокоманди. Моделі

мікрокомп’ютера відповідає

структура проілюстрована на рис.4.

Рис. 4

Регістри R0-R7

є регістрами загального призначення (РЗП). Регістр R8

- програмний лічильник (ПЛ). Регістри R9-R15

є

програмно доступними, причому R9,

R10 використовуються

для зберігання операндів після тактів ТО1 і ТО2, а

регістр R11

-

для запису результату після завершення такту ТО3.

Регістри RDI,

RDO призначені для

короткочасного зберігання даних під час запису в ОП та при читанні з неї.

Регістр RA

зберігає

адресу звернення до ОП.

Регістр команд RK

зберігає код команди.

Кнопковий регістр Rкн

фіксує адресу першого командного слова програми.

.

Мікропрограми операцій

.1 Арифметичні

операції

.1.1 Операція

«Додавання»

Цю операцію ВІС реалізує апаратно.

Мікропрограма операції показана на рис. 5.

Рис.5

пам'ять мікропрограма

алгоритм мікрокомп'ютер

Тривалість такту операції Т+=Р+*τ,

де Р+=1 - кількість процесорних тактів, τ-тривалість

процесорного такту.

Т+=τ

6.1.2 Операції

«Множення» і «Ділення»

У списку операцій ІМС ВС1 операції

«*» і «/» відсутні, тому в КП вони реалізуються мікропрограмо. Операції «*» і

«/» простіше виконувати над даними в прямому коді. Вважатимемо, що операнди

завжди додатні числа, що дозволяє нам дещо спростити загальний алгоритм

операцій «*» і «/».

6.1.3 Операція

«Множення»

Архітектура ВС1 орієнтована на

реалізацію першого алгоритму: множення починається з молодших розрядів

множника, сума часткових добутків зсувається вправо. Цьому алгоритму відповідає

мікропрограмна модель, зображена на рис.6.

Рис.6

Алгоритм множення в змістовній

формі.

. Співмножники розміщені в

регістрах R9, R10.

. Перевірка на рівність нулю

значень співмножників.

. Множник з R10

пересилається в регістр RQ.

. Сумі часткових добутків (R10)

присвоюємо

значення «0».

. Вміст RQ

зсуваємо вправо на один розряд.

. Аналізуємо молодший розряд

множника (стан тригера Т). Якщо Т=1,

до суми часткових добутків додається

множене (R9).

Якщо Т=0, до суми часткових добутків додається «0». Утворені суми часткових

добутків та множник в RQ

зсуваються вправо на один розряд.

. Пункт 6 повторяються для

всіх розрядів множника.

. Старша частина добутку

буде розміщена в R10,

молодша частина

добутку - в RQ.

Вважаємо, що старша частина 2n-розрядного

добутку (в R10)

дорівнює 0. Тому добуток буде n-розрядним

і пересилається з RQ

в R10.

. Кінець.

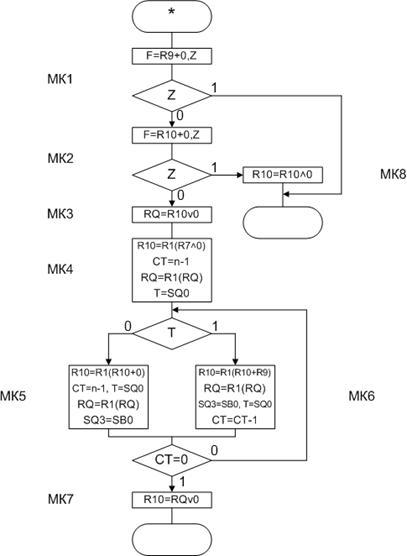

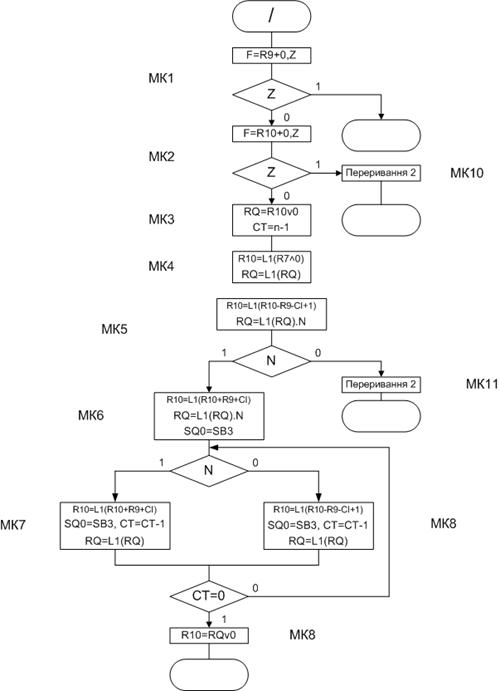

Граф мікропрограми (ГМП) операції

множення показаний на рис.7.

З нього випливає: кількість мікрокоманд

k*=7;

число процесорних тактів

, де p*min=1

, де p*min=1

p*max=4+(24-1)*1+1=28

=> p*=](28+1)/2[=15

Тривалість такту операції множення

буде Т*=Р**τ=15τ

Рис.7

6.1.4 Операція

«Ділення»

Використовуємо першу схему ділення:

ділене (залишки) зсуваються вліво, дільник - нерухомий. Мікропрограмна модель

операції зображена на рис.8. Вважаємо, що ділене має завжди формат слова. При

реалізації алгоритму ділене повинно представлятися у форматі подвійного слова.

Старшу частину діленого розміщуємо в R10,

молодшу - в RQ.

Тому вміст R7=0, a

RQ≠0.

Рис.8.

Реалізація алгоритму починається з

перевірки на рівність нулю діленого (R10)

та дільника (R9).

Якщо умови не виконуються, то ділене пересилається в RQ

і в R10

завантажується нуль. Таким чином формується ділене в подвоєному форматі.

У процесі операції в регістрах R10

i RQ

формується залишок і при їх подвоєнні звільняються молодші розряди RQ,

в які послідовно записуються значення цифр частки, починаючи зі старших

розрядів. Значення цифр частки протилежне знаку утвореного нового залишку. На

рис.8 відтворена схема формування подвоєного залишку і цифри частки. ГМП

ділення, що показаний на рис.9 реалізує алгоритм без відновлення залишку. З

нього випливає:

кількість мікрокоманд k/=7;

число процесорних тактів p/=](6+23+1+1)/2[=16

Тривалість такту операції множення

буде Т/=Р/*τ=14τ

Рис.9

6.1.5 Операція

умовного переходу JNZ

Операція JNZ

змінює

вміст ПЛ при значенні умови Z≠0.

ГМП показаний на рис.10. T=2τ.

Рис.10

6.1.6 Такт

збереження ТО3

Команда ST

- адресна і призначена для захисту вмісту регістра R10

в ОП або РЗП. ГМП показаний на рис. 11. T=3τ.

Рис.11

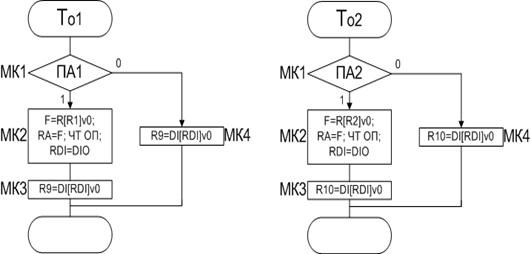

6.2 Мікропрограми

тактів Твк, ТО1, ТО2

.2.1 Такт

вибірки команди Твк

У такті вибірки команди код команди

вибирається із ОП на регістр RGK.

Адресацію команд забезпечує ПЛ. ГМП

такту показаний на рис.12. Т=2τ.

Рис.12

6.2.2 Такти

вибірки операндів То1, То2

В цих тактах операнди завантажуються

відповідно в регістри R9

та

R10.

Джерелом операндів можуть бути

регістр РЗП або комірка ОП, що визначається ознакою режиму адресації ПА1(ПА2).

ГМП тактів наведений на рис.13.

Т=](3+2)/2[=3τ

Рис.13

6.2.3 Мікропрограма

IPL

Мікропрограма IPL

забезпечує завантаження початкової адреси програми в ПЛ з кнопкового регістра Rкн.

ГМП зображений на рис.14.

6.3 Такт

декодування коду операції Тд

У такті Тд виконується ідентифікація

операції, яка представлена в полі

КОП регістра RGK.

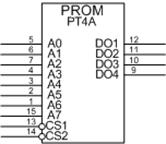

Декодер поля КОП реалізується як ПЗП (ROM)

(рис.15) і перетворює код операції в початкову адресу МП операції.

Код у полі КОП є адресою комірки

ПЗП, в якій записна початкова адреса

МП відповідної операції. У табл.3

наведені ці відповідності. З неї можна визначити такі параметри ПЗП як ємність q

та розрядність r

комірок .

ПЗП(q:r)=5x3

Для реалізації декодера вибираємо

ІМС КР556РТ4, що має організацію РТ4[q

x r]=256x4.

Таблиця 3

|

Адреса (КОП)

|

Початкова адреса МП

|

Операція

|

|

000

|

1

|

NOP

|

|

001

|

2

|

“+”

|

|

010

|

3

|

“*”

|

|

011

|

4

|

“/”

|

|

101

|

5

|

“JNZ”

|

.4

Розподіл адресного простору пам’яті

мікрокоманд

Керуючий пристрій мікрокомп’ютера

реалізує принцип програмованої логіки. Мікропрограми тактів операцій в

закодованій формі зберігаються в пам’яті

мікрокоманд. Розподіл адресного простору ПМК виконується з урахуванням

кількості мікрокоманд в ГМП тактів, способі реалізації декодування поля КОП, а

також організації ВІС ВУ4. Орієнтований розподіл мікрокоманд показаний у

табл.4.

Таблиця 4

|

Адреси

|

АП ПМК

|

Примітка

|

|

0

|

CJP16

|

IPL

|

|

1

|

CJP16

|

|

2

|

CJP49

|

“+”

|

|

3

|

CJP54

|

“*”

|

|

4

|

CJP59

|

“/”

|

|

5

|

CJP64

|

JNZ

|

|

6-10

|

To1

|

|

|

11-15

|

To2

|

|

|

16-18

|

Твк

|

|

|

19-24

|

То3

|

|

|

25-26

|

Т+

|

|

|

27-34

|

Т*

|

|

|

35-46

|

Т/

|

|

|

47-48

|

Tjnz

|

|

|

49

|

CJS6

|

Цикл “+”

|

|

50

|

CJS11

|

|

|

51

|

CJS25

|

|

|

52

|

CJS19

|

|

|

53

|

CJP16

|

|

|

54

|

CJS6

|

Цикл “*”

|

|

55

|

CJS11

|

|

|

56

|

CJS27

|

|

|

57

|

CJP19

|

|

|

58

|

CJP16

|

|

|

59

|

CJS6

|

Цикл “/”

|

|

60

|

CJS11

|

|

|

61

|

CJS35

|

|

|

62

|

CJP19

|

|

|

63

|

CJP16

|

|

|

64

|

CJS47

|

Цикл JNZ

|

|

65

|

CJP16

|

|

Для керування функціонуванням ВІС

ВУ4 використовуються мікрокоди,

символічні позначення яких наведені

у табл.4. Наприклад, запис CJP19

- це безумовний перехід до мікропідпрограми

операції збереження ST

за адресою 19. До загальної

кількості мікрокоманд мікропідпрограм додається ще одна - МК виходу з

мікропідпрограми.

З табл.4 випливає, що ємність

пам’яті МК = 66 комірок. Отже, розрядність адреси ПМК: nАПМК=]log266[=7

7. Структурна схема мікрокомп’ютера

Структурна схема мікрокомп’ютера

показана на рис.16. До його

складу входять: процесор, пам’ять,

пристрої вводу/виводу, генератор

тактових імпульсів.

Рис.16.

7.1

Процесор

Склад процесора: БМК, БОД,

блок регістрів.

7.1.1

Блок мікропрограмного керування

Регістр команд RGK призначений

для прийому, зберігання та видачі коду команди. Для реалізації RGK

використовуємо ІМС КМ1804ИР2.

Умовно-графічне позначення

регістра і поле мікрокоманди керування ним показано на рис.17.

Рис.17

Кількість ІМС ИР2, які

необхідні для реалізації регістра RGK, дорівнює:

n/nИР2=24/8=3

Перетворювач початкової

адреси ППА виконує функцію декодера КОП. Реалізується на ВІС КР556РТ4А

(рис.18).

Рис.18

Мультиплексор логічних умов MX ЛУ

призначений для комутації логічних умов (ЛУ) ПА1, ПА2, ПА3, N, Z, NZ, Т

на вхід “СС” ВІС

ВУ4. Для вибору ЛУ використовується поле MS в

полі мікрокоманди БМК. Розрядність поля визначається за формулою:

MS=]log2(L+1)[

де L -

кількість логічних умов. У нашому випадку L=7.

MS=]log2(7+1)[=3

Кодування логічних умов в

полі MS

наведено у табл.5.

Таблиця 5

|

К(MS)

|

ЛУ

|

|

000

|

“1”

|

|

001

|

N

|

|

010

|

Z

|

|

011

|

NZ

|

|

100

|

ПА1

|

|

101

|

ПА2

|

|

110

|

ПА3

|

|

111

|

Т

|

Мультиплексор MX

реалізується на ІМС КР1533КП5

.

.

Рис.19

Схема керування послідовністю

МК призначена для генерації адрес МК і реалізується на ВІС КМ1804ВУ4.

Рис. 20.

УГП СКПМК1804ВУ4

Мікрокоманда керування ВІС

ВУ4 має таку структуру:

|

16

|

ВУ4

|

0

|

|

3

|

I

|

0

|

6

|

A

|

0

|

2

|

MS

|

0

|

CI

|

CC

|

COM

|

|

16

|

|

13

|

12

|

|

6

|

5

|

|

3

|

|

2

|

|

|

1

|

|

|

0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пам’ять

мікрокоманд ПМК називається керуючою і призначена для зберігання мікропрограм

операцій. Орієнтована ємність ПМК 66 комірок. Розрядність комірок ПМК

відповідає розрядності МК. Реалізується як ПЗП (ROM)

на ВІС КР556РТ17, що має організацію 0,5Кх8. (Примітка: як буде визначено

пізніше, розрядність мікрокоманди становить nМК=56,

отже для реалізації запам’ятовуючого масиву ПМК потрібно буде взяти 56/8=7

мікросхем РТ17).

Рис. 21.

УГП ПЗП на ВІС

КР556РТ17

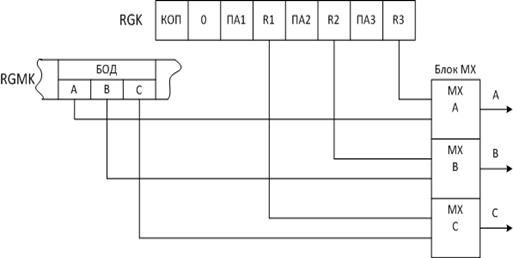

Блок мультиплексорів MX

призначений для комутації адрес звернень до регістрів загального призначення

(РЗП), що представлені в полях R1,

R2, R3

коду команди або адрес звернень до регістрів мікрокоманд, що відображені в

полях A,

B, C

регістра RGMK

(поле БОД). Структура блока MX

представлена

на рис.22.

Блок MX

реалізується на ІМС КР1533КП11.

Поле БМК коду мікрокоманди має таку

структуру:

|

20

|

БМК

|

0

|

|

RGMK

|

16

|

ВУ4

|

0

|

MX

|

MX

|

МХ

|

|

EN

|

WR

|

3

|

I

|

0

|

6

|

A

|

0

|

2

|

MS

|

0

|

CI

|

CC

|

COM

|

A

|

B

|

С

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.22

Функціональна схема блока MX

показана на рис.23.

Рис.23

7.1.2 Блок

регістрів

Блок регістрів забезпечує

короткочасне зберігання даних та адрес звернення до пам’яті. До складу блоку

входять наступні регістри.

Кнопковий регістр Rкн

призначений для завантаження та зберігання початкової адреси коду програми

ПА=010h.

Регістр Rкн

реалізується на ІМС КМ1804ИР2. Кількість ІМС ИР2 визначається розрядністю

фізичної адреси:

КRкн=nA/nИР2=16/8=2

Структура Rкн

показана на рис.24.

Включенням регістра керує поле МК Rкн.

Рис.24

Регістри даних RDI/RDO

служать для прийому/видачі з пам’яті/в пам’ять відповідно. Реалізуються на ІМС

КМ1804ИР2. Кількість ІМС становить 24/8=3. Керування функціями RDI/RDO

виконують відповідні поля МК.

Регістр адреси RA

призначений для прийому з БОД адреси, її зберігання та подачі на шину адресу.

Розрядність RA=nA=16.

Кількість ІМС: 16/8=2. Регістром керує відповідне поле МК.

Рис.25

Поле МК “RG” має

таку структуру:

|

6

|

RG

|

0

|

|

Rкн

|

5

|

RDI

|

4

|

3

|

RDO

|

2

|

1

|

RA

|

0

|

|

EN

|

WR

|

EN

|

WR

|

EN

|

WR

|

EN

|

|

|

|

|

|

|

|

|

|

|

|

|

|

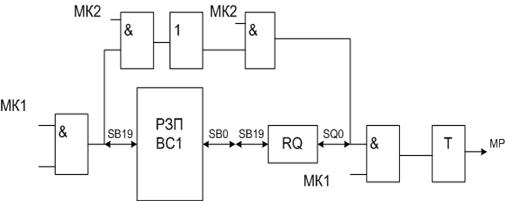

7.1.3 Блок обробки даних БОД

Блок призначений для обробки даних

та адресної інформації. Реалізується на ВІС ВС1 та ВР1. Кількість ВІС ВС1

визначається як max{n,

nA}.

Так як n=24

і nA=16,

то число ВІС ВС1

КВС1=n/nВС1=]24/4[=6

Для прискорення розповсюдження

переносу між ВІС ВС1 використовується ВІС ВР1.

Для зберігання ознак N,

NZ , Z,

T служить регістр

стану RGC.

Релізується на ІМС ИР2.

Для виконання операцій “*”

та ”/”

необхідна відповідна комутація виводів ВІС ВС1, яка показана на рис.26.

Рис.26

Мікрокоманда керування блоком

обробки даних має структуру:

|

24 БОД

0

|

|

24 \ ВС1

2

|

МК1 1

|

МК2 0

|

|

8 І 0

|

3 A 0

|

3 B 0

|

3 C 0

|

СІ

|

EN

|

|

|

|

|

|

|

|

|

|

|

7.2 Пам’ять

.2.1

Оперативна пам’ять

Оперативна пам’ять

має організацію (48Кх24).Реалізується

на динамічних ІМС К132РУ10А

з організацією (64Кх1).

Визначимо організацію ЗМ. Він має

площинну організацію t

x s,

де t

- кількість рядків, s

- кількість стовпчиків.

t

x s

= 48Кх24 / 64Кх1 = 1 х 24, t

= 1, s

= 24.

Функціональна схема RAM

мікрокомп’ютера

показана на рис.27.

Рис.27

.2.2

Постійна пам’ять

Постійна пам’ять має

організацію (16Кх24).

Реалізується на ВІС КМ555РР4, що мають організацію (8Кх8). Визначимо

організацію ЗМ. Він має площинну організацію t x s, де

t -

кількість рядків, s - кількість стовпчиків.

t x s = 16Кх24

/ 8Кх8 = 2 х 3, t = 2, s = 3.

Функціональна схема ROM

зображена на рис.28.

Рис.28

7.2.3

Дешифратор ПВВ

Дешифратор DC ПВВ

реалізується на ІМС КР1533ИД3.

7.2.4

Дешифратор DC АП

Функціональна схема

дешифратора DC АП

показана на рис.2. Для його реалізації в КП використовуються логічні елементи

серії КР1533.

7.3

Генератор тактових імпульсів (ГТІ)

В мікрокомп’ютері ГТІ

реалізується на ВІС КМ1804ГГІ, що дозволяє отримувати на своїх виходах

розподілені в просторі і часі послідовності тактових імпульсів CLK1, CLK2.

На рис.29

представлена схема підключення кварцового генератора та керування ГТІ. Входи “START” i “HLT”

використовуються для виставлення режимів роботи ГТІ “Робота” та “Призупинення”.

Рис.29

Генерація тактових імпульсів CLK1, CLK2

виконується в режимі “Робота”.

Такий режим задається в полі МК “ГГІ”

значеннями сигналів MST=1, MHT=0.

Режим “Призупинення” (зняття CLK1-CLK3)

установлюється значеннями MST=0, MHT=1.

8.

Формат мікрокоманди

Окремі поля мікрокоманди були

визначені на етапі розробки структурної схеми мікрокомп’ютера.

Загальний формат мікрокоманди показаний на кресленні 2.

9.

Закодована мікропрограма мікрокомп’ютера

Мікропрограма розміщується в

пам’яті МК і забезпечує керування пристроями мікрокомп’ютера відповідно до

семантики команди.

Закодована мікропрограма

розробляється з урахуванням формату МК, циклів команд, розподілу пам’яті МК, а

також використання ВІС ВС1 та ВУ4.

Мікропрограма наведена у

табл.6.

табл.6.

Висновки

Завданням даного курсового

проекту було спроектувати спеціалізований мікрокомп’ютер,

система команд якого однозначно визначається списком процедур (операцій),

необхідних для успішного рішення науково-технічної задачі.

Процес проектування був

розділений на два етапи: архітектурний та технічний. На архітектурному етапі

розроблений алгоритм рішення задачі(креслення 8). Ця схема деталізована до

арифметичних операцій (операторів присвоювання). Зі схеми випливає такий набір

арифметичних операцій: { + , * , / }.

Була обрана

опесердковано-регістрова адресація за виконанням необхідної умови для цієї

адресації.

Схема алгоритму

функціонування мікрокомп’ютера являє собою сукупність мікропідпрограм(креслення

7).

Розробивши мікропрограми

арифметичних, логічних операцій та основних тактів було виконано розподіл

адресного простору пам’яті

мікрокоманд.

Структурна схема мікрокомп’ютера

на кресленні 6.

Результатом технічного етапу

є принципова схема, наведена на кресленні 4.

Для керування блоками

мікрокомп’ютера

був розроблений формат мікрокоманди, наведений на кресленні 3.

Для рішення поставленої

задачі була розроблена мікропрограма (табл.6), поля якої заповнені згідно

формату мікрокоманди.

Список

літератури

1. Цифрові

електронні обчислювальні машини: Методичні вказівки до виконання курсових

проектів / Уклад.: Єфимець В. М., Жуков І. А., Іваськів Ю. Л. та ін. - К.: НАУ,

2011. - 52 с.

. Аверьянов

Н. Н., Березенко А. И., Борщенко Ю. И. и др. Микропроцессоры и

микропроцессорные комплекты интегральных микросхем. Том 2. - М.: «Радио и

связь», 2007. - 368 с.

. Дональд

Д. Гивоне, Роберт П. Россер. Микропроцессоры и микрокомпьютеры.

Вводный курс.: Пер. с англ. В. С. Штаркмана и Т. А. Шаргиной - М.: «Мир», 1983.

- 466 с.

4. Шило

В. Л. Популярные микросхемы ТТЛ. Серии: КР1533, КР1531, К531, К555, К155. - М.:

«Аргус», 2010. - 65 с.

. Полупроводниковые

БИС запоминающих устройств. Справочник под.редакцией Гордонова А. Ю. и Дьякова

Ю. Н. - М.: «Радио и связь»,1990. - 359 с.