Проектирование библиотек аналоговых приложений

Введение

Современные СБИС, изготавливаемые по субмикронным технологиям, содержат в

себе огромное количество блоков, таких как устройства памяти, процессорные

элементы, интерфейсы, цифровые и аналоговые узлы и так далее. Разработка таких

схем, несомненно, влечет за собой использование средств САПР (система

автоматизированного проектирования). И уже на этапе проектирования разработчик

сталкивается с необходимостью учета эффектов, связанных с уменьшением размеров.

Процесс уменьшения геометрических норм и увеличения сложности проектов

сопровождается усложнением системы правил проектирования [1]. В результате

планировка кристалла, содержащего, в том числе и аналоговые блоки, требует

огромной ручной работы для задания на верхнем уровне проектирования всего необходимого

множества ограничений. В этой связи становится актуальным вопрос о методологии

проектирования прецизионных аналоговых блоков. К таким блокам можно отнести

операционные усилители с малым смещением нуля, источники опорного напряжения,

точные компараторы в ЦАП (цифро-аналоговых преобразователь) и АЦП

(аналогово-цифровой преобразователь) и т.п.

Основная трудность разработки аналоговых блоков состоит не только в том,

чтобы создать устройство, принципиально реализующее заданную функцию, но еще и

в том, чтобы добиться требуемых параметров этого устройства [2]. Причем

реализация второго гораздо сложнее первого, так как параметры в первую очередь

зависят от технологического процесса изготовления микросхем.

Факторы, требующие учета при проектировании

Для производства аналоговых и цифро-аналоговых интегральных микросхем в

основном используется субмикронная КМОП-технология [3]. Для улучшения

параметров аналоговых блоков, для быстродействующих ЦАП и АЦП, а также

быстродействующих логических схем с большой нагрузочной способностью (мощные

выходные транзисторы) лучше всего использовать технологию БиКМОП. При

производстве аналоговых и смешанных ИС, содержащих высоковольтные прецизионные

аналоговые блоки (15-25 В), по КМОП-технологии широко используются поверхностные

биполярные структуры и высоковольтные транзисторы с разрывом на толстый окисел.

Можно использовать более дорогой и модифицированный КМОП-техпроцесс, в котором

дополнительно формируются высокоомные резисторы, конденсаторы со структурой

металл-диэлектрик-металл (МДМ), индукторы, биполярные диоды, транзисторы с

уменьшенными токами утечки, что очень актуально для разработки аналоговых

блоков. Однако для более эффективного использования преимуществ и компенсации

ряда недостатков современной КМОП-технологии рекомендуется следовать ряду

правил.

С уменьшением геометрических размеров и повышением быстродействия

проблема учета тонких физических эффектов на кристалле становится при

проектировании доминирующей. Упрощенные модели на большинстве этапов разработки

уже не годятся. Чтобы обеспечить надежное проектирование необходимы точные

модели и специальные средства анализа, учитывающие влияние таких факторов, как

сложные паразитные RC-структуры, падение напряжения в шинах питания,

индуктивность, электромиграция, высокочастотные эффекты, шум подложки [4].

При анализе требований к быстродействию нужно учитывать, что предельное

быстродействие аналогового блока ограничивается не нарушением функционирования,

а снижением соотношения сигнал/шум и соответствующим возрастанием искажений в

передаваемой информации.

Необходимо принимать во внимание влияние и таких дестабилизирующих

факторов, как помехи и разброс параметров КМОП-транзисторов. Задача очень

сложная, поэтому чаще всего уровень помех и разброс параметров транзисторов

оценивают раздельно и пытаются заранее применить все известные средства борьбы

с влиянием этих факторов, ограничиваясь заданными значениями быстродействия и

площади кристалла. После чего проводят оптимизацию электрической схемы с учетом

топологии и разброса параметров.

После корпусирования ИС параметры прецизионных аналоговых блоков,

расположенных внутри данной ИС, могут сильно ухудшиться. При проектировании ПАБ

следует учитывать паразитные свойства корпуса, а также увеличение плотности

выводов и потребляемой мощности, повышение рабочей частоты, температурные

эффекты и прочие параметры, зависящие от выбранного корпуса. При проектировании

системы питания особое значение имеют такие факторы, как падение напряжения в

шинах питания, увеличение плотности тока, электромиграция, области локального

перегрева. При проектировании межсоединений следует обратить особое внимание на

учет влияния механической и химической обработки пластины, влияние заливки

металлом, искажения сигнала в проводниках, шумы, импульсные помехи, электромиграцию,

индуктивность. При проектировании схематики прецизионных аналоговых блоков

необходимо учитывать эффекты на уровне транзисторов, такие как короткоканальные

эффекты, разброс параметров на кристалле, паразитные свойства, подпороговые

эффекты, использование транзисторов с разными пороговыми напряжениями, старение

и надежность. При проектировании особо чувствительных мест нужно учесть

паразитные свойства подложки, шумы, температурные эффекты.

Модели подложки должны позволять анализировать разнообразные

температурные эффекты и влияние цифрового шума на чувствительные аналоговые

блоки. Для моделирования надежности необходимы новые средства, учитывающие

значительный разброс параметров [5] полупроводниковых компонентов внутри

кристалла, особенности работы с несколькими значениями пороговых напряжений,

эффекты старения. Анализ надежности межсоединений должен учитывать влияние

процессов механической и химической обработки пластин на проводники и

окружающий диэлектрик, электромиграцию и искажения высокоскоростных сигналов в

проводниках.

Маршрут проектирования аналоговых ИС

аналоговый цифровой интегральный микросхема

Кратко маршрут проектирования [6] аналоговых ИС заключается в следующем :

) Постановка задачи, составление технического задания и формирование спецификаций.

) Системное проектирование - построение поведенческой модели системы на

высоком уровне абстракции с использованием языков программирования VerilogA, VerilogAMS, SystemVerilog, исследование параметров системы.

) Схемотехническое моделирование - разработка и создание

схемотехнического представления элементов ИС, использующихся в данном

технологическом процессе.

) Верификация и топология - разработка топологии, трассировка, проверка

правил проектирования топологии, экстракция паразитных параметров.

) Изготовление и тестирование ИС.

Разработка PDK

Изложенные выше аспекты проектирования АИС, маршрут проектирования, а

также факторы, которые необходимо учитывать при проектировании на субмикронном

уровне, позволяют составить полную картину всего того, что необходимо знать

разработчику технологических библиотек аналогового применения, разработчику PDK (Process Design Kit).

Для современных технологических процессов, знание и учет особенностей

проектирования на субмикронном уровне обязателен. Так, например, во время

разработки PDK на этапе создания моделей на

транзисторном уровне и проектировании топологии необходимо, если говорить о

МДП-транзисторах, предусмотреть возможность создания охранных колец заданной

конфигурации, форму, количество и конфигурацию пальцев, возможность создания

фиктивных элементов на краях массива транзисторов (dummy), обеспечить гибкость в размещение контактов к

поликремнию и диффузионным областям, возможность схлопывания транзисторов (auto-abutment) и т.д. с целью наилучшего

согласования МДП-транзисторов и широких возможностей для

дизайнеров-проектировщиков в дальнейшем на этапе схемотехнического

моделирования. На этапе составления правил проектирования разработчик PDK должен учесть влияние температурных

эффектов, короткоканальные и подпороговые эффекты, эффекты, связанные с

повышенным механическим напряжением, и т.д.

Вся эта информация заложена в модель параметризованных ячеек (PCell), содержащихся в PDK. Благодаря гибкости и наличию

переключателей (switch), созданных

на этапе разработки технологической библиотеки PDK, обеспечиваются широкие возможности для варьирования

параметров стандартных ячеек (транзисторов, резисторов, конденсаторов,

индуктивностей и т.д.), подразумевающих под собой также и параметризацию

топологического представления элемента. Что в дальнейшем помогает

дизайнеру-проектировщику ИС легко подстраиваться под требования заказчиков.

Для тестирования разрабатываемого PDK создаются тестовые ячейки по определенным правилам (testcase) для проверки и валидирования

создаваемых технологических библиотек; проводится схемотехническое

моделирования и верификация. Разработка тесткейсов подразумевает под собой

создание схемотехнического и топологического описания ячеек. Верификация

включается в себя проверку правил проектирования (DRC), сравнение разработанной

топологии с нетлистом или принципиальной электрической схемой (LVS), экстракция

паразитных параметров (RCX) из топологии и проведение сравнительного анализа

результатов моделирования с учетом паразитных параметров и без них.

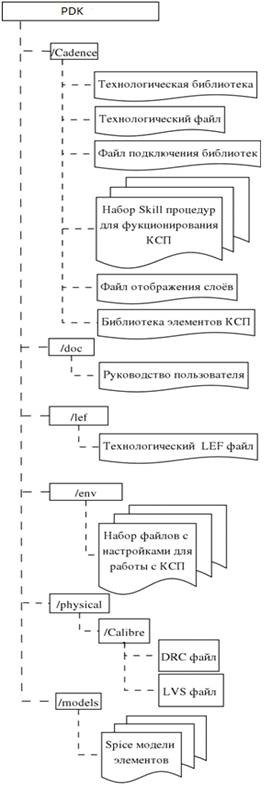

Рисунок 1. Состав PDK

Таким образом, структура PDK, представленная на Рис.1, включает в себя следующие

компоненты:

) библиотеки аналоговых примитивов: содержат различные

виды представлений примитивов - транзисторов, диодов, резисторов, конденсаторов

и т.д., которые используются на разных этапах разработки СБИС;

) технологическая библиотека: содержит технологический

файл с описанием слоев, файлы для проведения физической верификации,

экстракции, сравнения схемы с топологией и т.д.;

) Spice-модели: содержат модели для требуемых

симуляторов;

) документация: содержит документацию пользователя,

пояснения и комментарии к версии КСП и т.д.

) вспомогательные библиотеки, программы и скрипты,

необходимые для работы с КСП.

Применение САПР Cadence

в разработке PDK

Средства проектирования пакета Cadence [7,8] охватывают все стадии разработки - от проектирования

на системной уровне с использование IP-блоков до уровня логического, схемотехнического и топологического

проектирования СБИС, а также их корпусирования и формирования документации для

передачи в производство. Кроме того Cadence включает инструментальные средства проектирования печатных

плат, программно-аппаратные средства эмуляции для ускорения процесса

разработки.

Для разработки и тестирования PDK используются следующие средства Cadence:

) Virtuoso Schematic Editor - для создания принципиальной электрической схемы,

реализующей создаваемые тесткейсы.

) Virtuoso XL Layout Editor - для создания топологического описания тесткейса,

трассировки ячеек. Данный топологический редактор имеет удобный

пользовательский интерфейс, поддерживает иерархические проекты и параметризацию

ячеек, легко интегрируется с ведущими средствами проектирования различных

уровней. Встроенный язык управления SKILL позволяет настроить процесс

проектирования топологии под требования заказчика.

) Virtuoso Analog Design Environment (ADE) - для проведения моделирования и анализа схем,

создания нетлиста из схемотехнического описания. В зависимости от сложности и

объема решаемых задач ADE

может интегрировать различные системы аналогового моделирования (Spice, Spectre, Mica, UltraSim и др.). Кроме того ADE обеспечивает обратную аннотацию

паразитных параметров, экстрагируемых из топологического описания.

) Assura DRC/LVS и RCX - для проверки топологии на

конструктивно-технологические ограничения и соответствие исходной схеме,

экстракции паразитных параметров из топологии.

) QRC Extraction - для экстракции паразитных

параметров из топологии. В отличии от Assura RCX предоставляет

более широкие возможности (например, позволяет проводить подложечный шумовой

анализ).

) Virtuoso Power System - для моделирования эффектов IR-drop (падения

напряжения в шинах питания) и электромиграции.

Кроме того помимо Cadence Assura существует

необходимость также проводить DRC и LVS анализ с помощью средств Mentor Graphics (Calibre).

По мере разработки PDK

возникает необходимость в сравнении исправлений и обновлений, внесенных после

выпуска новой версии PDK,

или для создания глобального автоматического отчета по результатам работы DRC или LVS проверки одним из вышеизложенных инструментов. Для

этих целей используются скрипты, программы, написанные с использование языков

программирования Tcl, Skill, Shell и Perl

операционной системы Linux.

Заключение

Таким образом, в данной работе рассмотрены основные трудности и факторы,

с которыми сталкивается разработчик аналоговых и цифро-аналоговых устройств,

связанные с тенденцией современной электроники - минимизация элементной базы.

Эффекты, связанные с переходом в субмикронную область, требуют учета при

проектировании ИС.

Рассмотренные особенности маршрута проектирования аналоговых блоков СБИС

необходимо иметь ввиду при разработке Process Design Kit (PDK), включающего в себя спецификации на процессы,

технологические файлы, параметры приборов, командные файлы для проведения

физической верификации и экстракции параметров с использованием технологий Cadence, а также библиотеки

параметризованных приборов, построенные на основе языка SKILL, поддерживаемые технологическими

процесса. Также рассмотрены и проанализированы основное средства САПР Cadence, необходимые разработчику PDK.

Литература

[1]

Hastings A. The Art of Analog Layout. Prentice Hall. 2001.

[2] Адамов

Ю., Губин Я., Сибагатуллин А., Сомов О. Аналоговые блоки в системах на

кристалле // Электроника НТБ. 2004. № 8.

[3] Эннс В.

И., Кобзев Ю. М. Проектирование аналоговых КМОП ИС (Краткий справочник

разработчика). М.: Горячая линия - Телеком. 2005.

[4] Сорока Д.

Требования к современным САПР заказных СБИС //Электроника НТБ. 2004. №6

[5] Денисенко

В. Моделирование разброса параметров транзисторов в КМОП СБИС // Компоненты и

технологии. 2003. № 8.

[6] Бочаров

Ю.И., Гуменюк А.С., Симаков А.Б., Шевченко П.А. Проектирования БИС класса

“Система на кристалле”. Москва. 2008

[7] Иванов А.

Среда проектирования компании Cadence

// Электроника НТБ. 2004. № 5.

[8] Иванов А.

САПР Cadence как основа сквозного маршрута

проектирования электроники. 2009