Использование среды Cadence Virtuoso для проектирования интегральных микросхем

Національний

технічний університет України

«Київський

політехнічний інститут»

Кафедра

мікроелектроніки

КУРСОВА

РОБОТА

з курсу

”Моделювання технологій напівпровідникових приладів та інтегральних мікросхем”

на тему “Використання

середовища Cadence Virtuoso для проектування інтегральних мікросхем”

Студента Шевцова А.В.

Керівник доц. к.т.н. Татарчук Д.Д.

м.Київ - 2013

рік

Содержание

Аннотация

Список

условных сокращений

Вступление

.

Использование САПР в проектировании интегральных микросхем

.1

Современное положение в индустрии EDA

. Алгоритм

создания ИМС в среде Cadence Virtuoso

.

Иерархический подход к проектированию ИМС

.

Моделирование работы и параметры полученных устройств

4.1

Virtuoso Analog Design Environment- интерфейс и возможности

4.2

Результаты моделирования

Выводы

Список

литературы

Аннотация

В работе очерчены современные тенденции в области проектирования

интегральных микросхем и полупроводниковых приборов. Сделан акцент на

иерархическом подходе к проектированию. Именно он позволяет создавать

сверхбольшие ИМС.

Список условных сокращений

МДП(MOSFET) транзисторы типа

металл-диэлектрик-пп

БПТ (BJT)

биполярные транзисторы

КМДП (CMOS)

комплементарные МДП

ІМС (ІС)

интегральная микросхемалогический элемент И-НЕТтехнология локального окисления

кремния

САПР система

автоматизированного проектированияСАПР в электронике

Вступление

Принятая на сегодняшний день модель развития промышленности предполагает

широкую роботизацию‚ создание гибких автоматизированных производств и отводит

особое место микроэлектронике как средству и материальной базе реализации

целевых программ в области автоматики и робототехники, вычислительной техники,

механизации и автоматизации ручных операций во всех отраслях промышленности.

Особая роль отводится микроэлектронике в развитии вычислительных средств.

Но сложность современных ИМС требует новых подходов проектирования

Системы автоматизированного проектирования (САПР) уже давно являются

неотъемлемой частью современного производства. Образовавшись в виде средств

решения проектных задач, имеющих четко выраженный расчетный характер, системы

автоматизированного проектирования прошли несколько стадий своего развития и

выросли до уровня технологий, охватывающих больше, чем просто проектирование.

Однако современный рынок проектных работ требует дальнейшей модернизации и

перехода на новые технологии. Заказчики всё чаще обращают внимание не только на

стоимость проекта, но и на техническое оснащение организации, ее способность в

сжатые сроки выпустить качественный проект. При этом от предприятия требуется

применение самых современных методов и подходов к созданию и поддержке изделия

на всех стадиях его жизненного цикла. Поддержка жизненного цикла изделия, PLM

(Product Lifecycle Management), комплексная автоматизация и использование

единого информационного пространства становятся ключевыми при выборе средств

автоматизации.

Проведение комплексной автоматизации, обеспечивающей не только потребности

максимального количества проектных специальностей, но и корректную передачу

данных между рабочими местами различного назначения, создание единого

информационного пространства является первоочередной задачей проектных

организаций. Как результат, повышается качество выпускаемой документации,

уменьшается количество ошибок, сокращаются сроки проектирования, а значит,

повышается конкурентоспособность предприятия. При этом задачи единой среды

проектирования сводятся к обеспечению коллективной работы проектно-конструкторских

подразделений над проектом, хранению и поиску информации в электронных архивах,

повторному использованию отработанных и проверенных технических решений,

хранящихся в архиве, а также исключению ошибок за счет устранения нескольких

источников для хранения одной и той же информации.

1. Использование САПР в проектировании интегральных микросхем

Развитие электроники неразрывно связано с развитием средств

автоматизированного проектирования электронных устройств. Без работы

специалистов этой области уже невозможно представить проектирование и

производство современных микроэлектронных систем. Сегодня индустрия средств

автоматизированного проектирования электроники (Electronic Design Automation -

EDA) - неотъемлемая часть электронной промышленности. Ежегодный оборот

EDA-индустрии превышает четыре миллиарда долларов.

В конце 80-х годов интегральные микросхемы настолько усложнились, что

создание описания принципиальной схемы (как с помощью схемотехнического

редактора, так и в текстовом виде) стало существенной проблемой. Были

разработаны первые инструменты, которые позволяли из описания на уровне

регистровых передач (Register Transfer Level - RTL, языки Verilog или VHDL),

уже применявшихся в моделировании, автоматически синтезировать описание принципиальной

схемы на уровне логических элементов. В 1987 году компания Synopsys вышла на

рынок с соответствующим продуктом Design Compiler, за ней вскоре последовал

AutoLogicот фирмы SCS-Mentor Graphics. Специалисты Synopsys вовремя оценили

преимущества технологии автоматического синтеза для рынка СБИС на базе

стандартных библиотек логических элементов (ASIC). Использование таких средств

позволяло разработчикам проводить независимое проектирование ИС на верхнем

уровне, осуществляя разработку описания на языках Verilog или VHDL и его

верификацию средствами логического моделирования. После автоматического синтеза

результаты проектирования в виде описания принципиальной схемы на уровне

логических элементов передавались компании-производителю ИС.

Компания производитель выполняла физическое проектирование

(размещение/трассировка, контроль правил проектирования и соответствия

электрической схеме, подготовка данных для изготовления фотошаблонов), а также

производство и тестирование. Таким образом, до середины 90-х годов на EDA-рынке

в сфере физического проектирования и проектирования аналоговых и смешанных ИС

лидировала компания Cadence, а в области логического синтеза господствовала

Synopsys.

1.1 Современное положение индустрии

В середине 90-х годов появились первые интегральные схемы с нормами

проектирования 0,5 и 0,35 мкм. Возникла необходимость учета различных тонких

физических эффектов. Увеличилась суммарная длина проводников, проводники стали

существенным источником запаздывания сигналов. Применявшаяся до сих пор

методология проектирования ASIC достигла предела своих возможностей, поскольку

определяющим фактором стало качественное проектирование топологии схемы.

Компания Cadence воспользовалась имеющимися наработками в сфере

размещения/трассировки и представила разработчикам новый метод проектирования

топологии (back-end), который позволял специалистам в области проектирования

верхнего уровня (front-end) использовать технологии предварительного размещения

(1992 год - Preview, 1996 год - Design Planner). С усложнением проектов ИС

решающее значение приобрело использование оптимальной методологии

проектирования. Эта тенденция развития EDA-индустрии была вовремя замечена, и с

1994 года компания Cadence предлагает пользователям не только программные

средства, но и поддержку оптимальной методологии проектирования, а также

сервисные услуги.

С переходом на субмикронные технологии стали всё чаще появляться

отдельные независимые дизайн-центры (fabless company), которые приобретали

EDA-средства, необходимые для обеспечения процесса проектирования ИС (Customer

Own Tooling, так называемая COT-мoдель). Дизайн-центры осуществляли полный цикл

разработки СБИС с использованием собственной методологии и IP-библиотек, а

заказы на производство размещали на таких фабриках, как TSMC, UMC и Chartered.

С возникновением этой бизнес-модели для EDA-индустрии открылась ещё одна

рыночная ниша, в которой можно было предлагать не только продукты, но и

технологии проектирования и сервисные услуги.

Выход на рынок среды проектирования Virtuoso компании Cadence в начале

90-х годов позволил на порядок повысить производительность заказного

проектирования. Среда Virtuoso постоянно пополнялась большим числом

инновационных продуктов. Например, в 1993 году появилась система аналогового

моделирования Spectre, в 1995 году были добавлены средства моделирования

нелинейных радиочастотных (RF) схем, а в 2000 году - средства Verilog-AMS -

единого инструмента для совместного цифроаналогового моделирования. Следующий

шаг в сторону модернизации был сделан в 1997 году благодаря технологии

IC-Craftsman, которую фирма Cadence приобрела при поглощении компании Cooper

and Chyan (CCT).

На рубеже тысячелетий началось производство с применением технологических

норм 130, 90 и даже 65 нм. При использовании таких технологий решающими факторами

успеха становится учет паразитных явлений и оценка искажения сигнала. Это

означает, что должна учитываться реальная конфигурация соединений. Средств

физического синтеза уже недостаточно для получения требуемого результата.

Возникла необходимость разработки новых методов. В 2002 году компания Cadence

поглотила фирму SiliconPerspective, реализовавшую в продукте First Encounter

концепцию виртуального прототипа. Система First Encounter фактически стала

стандартом для проектирования с использованием нанометровых технологий.

В настоящее время EDA-индустрия развивается с учётом требований

нанометровых технологий и методологии проектирования

"система на кристалле" (systems-on-chip, SoC). Системное

проектирование, проектирование схем малой мощности, проектирование с учетом

требований производства, интеграция систем - вот лишь некоторые из тех

областей, которым разработчики в ближайшие годы должны будут уделить внимание.

2. Алгоритм создания ИМС в среде Cadence Virtuoso

Технология Cadence охватывает практически все уровни разработки сложных

систем - от системного уровня, свойственного разработчикам аппаратуры, до

уровней логического, схемотехнического и топологического проектирования СБИС,

их корпусирования, а также разработки печатных плат, на которых эти СБИС будут

монтироваться.

В целом проектирование СБИС в среде Cadence включает следующие этапы:

• системное проектирование - построение модели системы на высоком уровне

абстракции с использованием языков программирования C/C++ и SystemC, разбиение

на программные и аппаратные модули, исследование параметров системы, получение

спецификаций (набора требуемых параметров) на программные и аппаратные блоки;

• аппаратное проектирование и верификация - разработка на основе

спецификации поведенческих моделей отдельных блоков системы с использованием

языков Verilog/VHDL, реализация проекта в базисе библиотек производителя ИС,

проверка программно-аппаратной реализации на соответствие спецификациям,

полученным на системном уровне;

• физическое прототипирование - предварительное размещение элементов,

оценка потребляемой мощности, планирование шин питания и иерархии тактовых

сигналов, качественная оценка возможных искажений сигнала;

• проектирование и верификация топологии кристалла - разработка топологии

заказных блоков, трассировка на уровне ячеек, проверка правил проектирования

топологии, экстракция паразитных параметров.

интегральный

микросхема полупроводниковый транзистор

3. Иерархический подход в проектировании ИМС

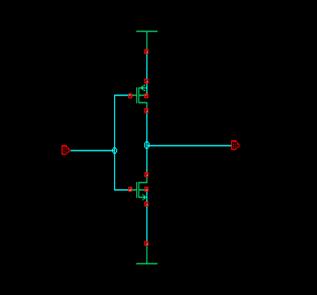

Исходным элементом при проектировании были выбран МДП-транзисторы p-n -

типа с встроенным каналом

Использование графического редактора Cadence Composer Schematic Editor,

является традиционным для описания проектируемого устройства на транзисторном

уровне. Редактор предоставляет возможность визуального размещения основных

компонентов схемы (транзисторов, диодов, конденсаторов, катушек индуктивности),

вспомогательных компонентов (источников постоянного тока и напряжения,

источников малых сигналов), а также контактов (пинов), использующихся при

иерархическом представлении сложных схем, и соединения элементов между собой.

Результатом работы в Composer Schematic Editor является создание таблицы

соединений схемы, записи которой служат в дальнейшем входными данными для

других инструментов САПР Cadence. Очевидно, что на следующих этапах разработки

устройства может потребоваться изменение начального представления схемы. В этом

случае будут откорректированы и записи таблицы соединений.

Рассмотрим реализацию логических элементов с использованием

NMOS-транзисторов и PMOS-транзисторов.

Рис. 2 а) Схемная реализация инвертора б) схемная реализация логического

элемента И-НЕ

4. Моделирование работы и параметров созданного прибора

4.1 Virtuoso Analog Design Environment - интерфейс и возможности

Моделирование или анализ работы устройства, представленного

принципиальной электрической схемой, проводится в среде Analog Design

Environment. Как было отмечено ранее, входными данными для нее являются записи

таблицы соединений схемы, на основании которых строятся системы

дифференциальных уравнений. В ходе решения данных систем могут быть получены

величины параметров, характеризующих работу моделируемого устройства.Design

Environment поддерживает моделирование с использованием различных уровней

абстракции моделей - от чисто поведенческого на верхнем системном уровне до

точных, откалиброванных по экспериментальным данным на нижнем, наиболее

детальном уровне. Уровни абстракции физического дизайна меняются от оценочных

на ранних стадиях, до финальных трассировки и экстракции. Кремниевый анализ,

основанный на расширенных моделях полупроводниковых приборов, прецизионной

экстракции и средствах анализа, дают адекватную информацию в течение всего

процесса проектирования.

В зависимости от сложности и объема решаемых задач, Vittuoso ADE (Analog

Design Environment) может интегрировать различные системы аналогового

моделирования (Spice, Spectre, UltraSim, Multi-mode Simulation), обепечивать

обратную аннотацию паразитных параметров, экстрагируемых с помощью Assura RC,

поддерживать кросс-пробинг между схемным вводом (Virtuoso Schematic Editor),

топологическим редактором (Virtuoso Layout Editor) и системой анализа

результатов моделирования.

Рис. 4 а) Основные компоненты среды проектирования Virtuoso ADE

б) Диалоговое окно для выбора параметров и методик моделирования

5. Достижение предела классических подходов с использованием

ОДУ. Пути решения кризиса

Классические программы моделирования аналоговых электронных схем,

обеспечивают хорошую сходимость решения в большинстве случаев и гарантируют

достаточную точность. Однако, постоянный рост сложности и объемов проектов БИС

привел к увеличению размеров схем до десятков и сотен миллионов узлов. Как

следствие, производительность классических программ моделирования, построенных

на традиционном подходе составления и решения системы ОДУ с применением методов

разреженных матриц, стала явно недостаточной для решения системы уравнений, описывающей

всю схему.

Подходы, применявшиеся несколько лет назад, состоят в расчете фрагментов

схем, базовых ячеек или в комбинированном применении логических и временных

расчетов совместно с моделированием аналоговых фрагментов схем на уровне

транзисторов. Широкое распространение нашло также макромоделирование.

В последние годы, интенсивно начали развиваться программы моделирования

нового поколения, так называемые «быстрые симуляторы» . Их применение дает

качественный скачок в производительности. Появилась возможность моделировать

БИС объемом в десятки и сотни миллионов узлов с точностью и требованиями к

вычислительным ресурсам, близкими к традиционным программам моделирования.

Решение, предлагаемое Cadence на данном сегменте рынка, - платформа

Virtuoso и система FastSPICE Ultrasim . Наряду с известными системами

моделирования, Ultrasim интегрирован в общую среду разработки Virtuoso и дает

возможность быстро получить решение с приемлемой точностью при возрастании

сложности проекта на несколько порядков.

Технические требования к аналоговым, заказным цифровым, радиотехническим

и смешанным проектам росли экспоненциально в последнее десятилетие (рис. 2).

Экономические факторы и конкуренция на рынке электроники вынуждают

разработчиков применять новые технологии и объединять прежде независимые блоки

на одном кристалле (System-On-Chip, SOC). Многие производители переходят на

современные технологии проектирования по нормам 0.13 мкм - 65 нм, и совмещают

аналоговое проектирование, с нанометровыми цифровыми дизайнами. Более того,

основой цифрового проектирования является использование библиотек стандартных и

специализированных заказных блоков, разрабатываемых с применением средств

аналогового моделирования.

Рис. 5 Взаимосвязь технологии, сложности и стоимости проекта

Платформа для заказного проектирования Virtuoso [2] является понятной

системой для быстрого и точного проектирования, оптимизированной для технологии

meet-in-the-middle, например Analog Custom Design (ACD).

Рис 6 Процесс проектирования с помощью платформы Vituoso

В Virtuoso входит среда, определяемая спецификацией, многорежимное

моделирование, имеющее общий синтаксис, модели и системы уравнений, значительно

ускоренные слои и объединенная на уровне всего кристалла, а также среда

смешанного моделирования.поддерживает моделирование с использованием различных

уровней абстракции моделей - от чисто поведенческого на верхнем системном

уровне до точных, откалиброванных по экспериментальным данным на нижнем,

наиболее детальном уровне. Уровни абстракции физического дизайна меняются от

оценочных на ранних стадиях, до финальных трассировки и экстракции. Кремниевый

анализ, основанный на расширенных моделях полупроводниковых приборов,

прецизионной экстракции и средствах анализа, дают адекватную информацию в

течение всего процесса проектирования. В зависимости от сложности и объема решаемых

задач, Vittuoso ADE (Analog Design Environment) может интегрировать различные

системы аналогового моделирования (Spice, Spectre, UltraSim, Multi-mode

Simulation), обепечивать обратную аннотацию паразитных параметров,

экстрагируемых с помощью Assura RC, поддерживать кросспробинг между схемным

вводом (Virtuoso Schematic Editor), топологическим редактором (Virtuoso Layout

Editor) и системой анализа результатов моделирования.

Платформа Virtuoso может работать с базой данных Cadence CDBA или с базой

OpenAccess. С этой платформой, возможно быстрое проектирование с высоким

выходом годных для геометрий от 1 мкм до 90 нм и менее.

Выводы

С использованием современной FastSPICE технологии Virtuoso UltraSim,

система моделирования позволяет выполнять высокопроизводительное, аналоговое

или смешанное моделирование всей системы. Поддержка многих языков описания

объектов обеспечивает независимость языка и уровня абстракции в методологии

проектирования. Обобщенная реализация полупроводниковых приборов в системах моделирования,

входящих в платформу Virtuoso, гарантирует высокую точность результатов. С

учетом RC-редукции, с помощью UltraSim и Virtuoso стало возможным решение ранее

недоступных задач полной и точной верификации проекта после фазы разработки

топологии на нанометровых технологиях.

Платформа заказного проектирования Vittuoso легко интегрируется в единый

маршрут проектирования с платформой функциональной верификации Incisive. Фирма

Cadence обеспечила интеграцию новой системы на уровне plug-and-play и

предоставила разработчикам возможность использования современных средств

аналогового моделирования и заказного проектирования в рамках единой

методологии разработки СБИС.

Список литературы

1. Жан

М.Рабаи Цифрофые интегральные схемы 2-е изд 2007 год

. Жмурко

С.А..Разработка подсистемы поиска информации в гетерогенных САПР на основе

многоагентных систем - дис. 2010г.

. Ф.Томас

А Иванов САПР микроэлекроники - ж. Электроника №3 2006г.

. А

Иванов Среда проектирования компании Cadence - ж. Электроника №5 2003г.

. Шелохвостов

В.П. Проектирование интегральних микросхем 2008г.