Средства отладки электронных схем

Министерство Промышленности и Энергетики РФ

Реферат

Средства отладки электронных схем

Выполнил студент 412

группы:

Боровков И.А.

Проверил:

Волков А.В.

Иваново

2004

Содержание:

Введение 3

1.

Средства отладки для микроконтроллеров семейства HC05

3

1.1

Внутрисхемные симуляторы 5

1.2

Внутрисхемные эмуляторы 7

1.3

Программаторы 10

1.4

Средства разработки третьих фирм 11

2.

Отладочные средства БИС 12

2.1

Средства разработки электронных схем 12

2.2

Прототипные платы схем программируемой логики с ISA

13

2.3

Прототипные платы схем программируемой логики с PCI 13

2.4

Платы разработчика для схем программируемой логики с PCI 14

2.5

Оборудование для контроля и отладки проектных плат 15

2.6

Комплекс средств тестирования методом граничного

сканирования JTools 16

2.7

Комплекс средств тестирования методом граничного

сканирования (дополнительно) 17

Заключение 18

Список

используемой литературы 19

Введение

Сегодня

промышленность шагнула далеко вперед в производстве интегральных схем, это

видно, из того, что размеры микросхем уменьшаются, а производительность и

характеристики возрастают в положительную сторону. Но в связи, с этим,

возникает один недостаток, микросхемы усложняются по своей структуре и

функциональному предназначению. И как следствие возникает проблема контроля

выхода годных интегральных схем и выявление причин возникающих неполадок.

Денежные и трудовые затраты на тестирование

сложных интегральных схем с привлечением контрольно-измерительной аппаратуры

может во много раз превышать стоимость интегральной схемы из-за длительности

процесса тестирования и сложности его реализации. Производить тестирование на

модели разрабатываемой интегральной схемы существенно удешевляет процесс

тестирования и сокращает время его проведения.

Реальные

образцы создаются на основе проекта интегральных схем, разработанного на этапах

логического и топологического проектирования. И затем, каждый образец должен

пройти функциональный контроль, устанавливающий правильность его работы.

При тестировании на математической модели или реальном образце

обнаруживаются неисправности интегральной схемы путем анализа состояний ее

выхода на определенных наборах входных сигналов. Успешное решение задачи тестирования

интегральной схемы на всех стадиях проектирования и изготовления определяет в

конечном итоге ее важнейшие характеристики, такие как: 1. бездефектность

проектирования; 2. надежность работы; 3. устойчивость работы; 4. стоимость

образцов; и др.

Можно

выделить два вида тестирования интегральных схем:

1.

функциональное тестирование, осуществляемое на всех этапах

разработки логической схемы;

2.

функциональный контроль правильности работы образцов интегральных

схем после их изготовления.

В данном реферате будут рассмотрены средства отладки для

микроконтроллеров семейства HC05 и БИС PLD FLEX10K и др.

1. Средства отладки для

микроконтроллеров семейства HC05

Микроконтроллеры

семейства HC05 фирмы MOTOROLA являются относительно новыми для российского

разработчика. Несмотря на то, что информация о МК семейства HC05 присутствует в

тех или иных изданиях уже порядка пяти

лет, а подробная техническая документация в большом количестве содержится на

серверах компании, использование этих МК в разработках российских инженеров

по-прежнему ограничено. Данное обстоятельство является всего лишь

подтверждением аксиомы о том, что МК без средств отладки и программирования

являются схемами абсолютно бесполезными с практической точки зрения.

Недоступность в течение достаточно длительного времени российскому разработчику

дешевых средств поддержки разработки для 8-разрядных МК фирмы МотоRоLа часто

оказывается решающим фактором при выборе элементной базы новой разработки.

Число альтернативных вариантов МК, которые могут обеспечить

примерно равные технические характеристики создаваемого изделия, среди

8-разрядных МК значительно больше, чем при ведении разработки на основе 16- и

32-разрядных МК. Поэтому однозначный выбор 8-разрядного МК редко диктуется

только техническими условиями, за исключением случаев, требующих предельного

быстродействия. С экономической точки зрения, выигрыш в цене на комплектующие

при замене одного 8-разрядного МК на другой с близкими техническими

характеристиками оказывается не столь существенным по сравнению с

необходимостью обеспечения предельно коротких сроков разработки изделия. Именно

в этом случае особое значение приобретают “степень освоения” разработчиком

выбранного МК и предварительные программные наработки. Именно в этом случае

сказывается долгое отсутствие на российском рынке дешевых инструментальных

средств разработки и бесплатных программных симуляторов с небольшим набором

функций. В настоящий момент, благодаря программе “NO EXUSES”, такое положение

дел меняется коренным образом.

МК семейства HC05 имеют общее процессорное ядро, но

существенно различаются объёмом резидентного ПЗУ программ и набором

периферийных модулей. С точки зрения методологии отладки, их можно условно

разделить на две группы. Маловыводные МК серий K, J, P (число выводов корпуса от

16 до 28) имеют ПЗУ программ от 1 до 4,6 Кбайт и малое число периферийных

модулей. Объём резидентного ПЗУ не предполагает использования этих МК для

сложных задач, поэтому прикладная программа может быть написана на языке

Ассемблер, и весьма вероятно, что при отладке можно будет обойтись без

инструментальных средств реального времени. Ко второй группе относятся МК с

объёмом памяти программ от 8 до 16 Кбайт с развитым набором периферийных

модулей (серии B, C, L). Эти МК требуют более развитых средств отладки.

Для МК семейства НС05 фирма МотоRоLа

предлагает программно-аппаратные средства разработки следующих классов:

·

программные симуляторы;

·

внутрисхемные симуляторы ICS (In-Circuit Simulator);

·

внутрисхемные эмуляторы типа MMEVS (Motorola Modular Evaluation

System);

·

внутрисхемные эмуляторы типа MMDS (Motorola Modular Development

System);

·

программаторы.

1.1 Внутрисхемные симуляторы

Безусловно, самой дешевой технологией

отладки, знакомой всем отечественным разработчикам со стажем, является набор

“Ассемблер – Симулятор – Программатор”. Учитывая небольшой объём памяти

маловыводных МК и дешевизну МК этих серий, такой путь на первом этапе мог бы

считаться вполне приемлемым. Однако, драйверы программирования для широкого

набора МК Motorola редко присутствуют в отечественных универсальных

программаторах, что часто делает этот путь практически нереализуемым.

Поэтому бесплатные программные

симуляторы, присутствующие на сервере

#"66835.files/image001.jpg">

|

Cостав средств:

- платы разработчиков для схем программируемой логики;

- прототипные платы для БИС фирмы Altera;

- специальное тестирующее оборудование;

- программное обеспечение;

- методическое

обеспечение.

|

Применение

средств обеспечивает быструю реализацию проектов и контроль их

работоспособности на всех этапах изготовления и внедрения, включая отладку

образцов, входящих в состав конечной аппаратно-программной системы.

Основные характеристики:

- стандарт интерфейсных плат -

ISA, PCI;

- PLD семейства - MAX7000S, FLEX10K, ACEX;

- сложность реализуемых

проектов - 10 - 100 тыс. вентилей.

На отечественном рынке не имеется аналогичного комплексного

подхода к проблемам проектирования плат расширения.

Особенности и преимущества:

·

эффективность: учет специфики

отлаживаемого оборудования;

·

стоимость: значительно меньшая,

чем у традиционных средств отладки программно-аппаратных систем или у

зарубежных аналогов;

·

передачу конкретных

схемотехнических решений для определенных областей использования;

2.2 Прототипные платы схем

программируемой логики с

интерфейсом ISA

Прототипные

платы программируемой логики с интерфейсом ISA позволяют отлаживать широкий

круг пользовательских проектов, ориентированных на БИС PLD FLEX10K (Рис.2).

Рис. 2

Плата программируемой логики с интерфейсом ISA

Особенности реализации:

·

допустимость отладки больших и

сложных пользовательских проектов (так как логическая мощность системных БИС

составляет 10, 20 или 30 тысяч эквивалентных логических вентилей, а в ближайшее

время превысит 70 тысяч вентилей);

·

возможность использования в

проектах встроенных сверхоперативных блоков ОЗУ;

·

обеспечение простоты и легкости

смены пользовательских проектов при реконфигурировании через интерфейс ISA;

·

отсутствие ограничений на

количество циклов реконфигурирования;

·

возможность загрузки

конфигурации из схемы постоянной памяти;

·

предоставление средств

организации гибкого взаимодействия между аппаратными ресурсами PLD и

программным обеспечением ПЭВМ;

·

допустимость разнообразных

способов организации взаимодействия между аппаратными ресурсами PLD и

программным обеспечением ПЭВМ.

2.3 Прототипные платы схем программируемой логики с

интерфейсом PCI

Прототипные платы программируемой логики с интерфейсом

PCI позволяют отлаживать широкий круг пользовательских проектов,

ориентированных на БИС PLD FLEX10K.

Рис.3 Прототипные платы

|

|

Семейство в своей основе

содержит:

·

четыре БИС сверхоперативной памяти (цикл обращения не более

15 нсек).

По функциональному

назначению схемы PLD распределяются:

- интерфейсная БИС типа

FLEX10K - EPX10K30QC240-3;

- системная БИС типа FLEX10K

- EPX10K30ATC144-4,

- управляющая БИС типа MAX7000S - EPM128STC100-6.

|

Особенности реализации:

·

допустимость отладки больших и

сложных пользовательских проектов до 60 тысяч вентилей;

·

возможность использования в

проектах встроенных сверхоперативных блоков ОЗУ;

·

возможность использования в

проектах блоков ОЗУ большой емкости (до 128K 32-разрядных слов);

·

обеспечение простоты и легкости

смены пользовательских проектов, загружаемых в системную БИС через интерфейсную

БИС;

·

отсутствие ограничений на

количество циклов реконфигурирования;

·

обеспечение загрузки

конфигурации интерфейсной БИС из схемы постоянной загрузочной памяти;

·

возможность закрытия битом

секретности доступа к содержимому внутреннего ОЗУ платы.

2.4

Платы разработчика для схем программируемой логики с интерфейсом PCI

Платы

разработчика для схем программируемой логики с интерфейсом PCI позволяют

отлаживать широкий круг пользовательских проектов, ориентированных на БИС PLD

ACEX.

Рис. 3 Плата программируемой логики с интерфейсом PCI

Семейство в своей основе содержит:

- схему программируемой логики;

- две БИС сверхоперативной памяти (цикл обращения

не более 15 нсек).

Особенности реализации:

·

допустимость отладки больших и

сложных пользовательских проектов до 100 тысяч вентилей;

·

возможность использования в

проектах встроенных сверхоперативных блоков ОЗУ;

·

возможность использования в

проектах блоков ОЗУ большой емкости (до 128K 16-разрядных слов);

·

обеспечение простоты и легкости

смены пользовательских проектов, загружаемых в БИС;

·

наличие монтажной зоны для

размещения ИС пользователя;

·

возможность использования дополнительных

плат по мезонинной технологии;

·

обеспечение загрузки

конфигурации БИС из схемы постоянной загрузочной памяти.

2.5

Оборудование для контроля и отладки проектных плат

Оборудование

для контроля и отладки проектных плат с интерфейсом по стандарту ISA или PCI

представляют собой платы-удлинители для соответствующих интерфейсных плат, у

которых каждая линия интерфейса имеет соединение с контролирующей БИС PLD.

Рис. 4

Оборудование для контроля и отладки проектных плат

Если ИС

проектируемой платы поддерживают граничное сканирование (BST) через JTAG интерфейс,

то разработанное на кафедре ПО позволит с помощью платы отладчика до установки

разрабатываемой платы в ПК найти ошибки как в межсоединениях этих ИС между

собой, так и в их соединениях с разъемом компьютера. Та же плата отладчика с

другим вариантом ПО позволяет имитировать поведение любой мыслимой и немыслимой

комбинации управляющих сигналов интерфейсной шины.

Плата отладчика может оказать существенную помощь

разработчику аппаратуры и в тех случаях, когда штатная работа платы расширения

нарушается трудно обнаруживаемыми сбоями. Встраивание в схемы PLD фрагментов

таких отладочных средств, как следовые ОЗУ, логические анализаторы,

разнообразные аппаратные ловушки позволяет разработчику облегчить задачу

нахождения причины возникающих сбоев или перемежающихся.

2.6 Комплекс средств тестирования

методом граничного сканирования JTools

Функциональные возможности

комплекса базируются на интерфейсе JTAG и технологии граничного

сканирования (Boundary Scan Testing), которые широко поддерживаются ведущими

производителями БИС (Intel, Motorola, Altera, Xilinx, Atmel, TI, и другими).

Функциональные возможности

комплекса базируются на интерфейсе JTAG и технологии граничного

сканирования (Boundary Scan Testing), которые широко поддерживаются ведущими

производителями БИС (Intel, Motorola, Altera, Xilinx, Atmel, TI, и другими).

Состав комплекса:

- универсальный

загрузочный кабель;

- резидентная

программа управления кабелем BitMaster;

- программа

тестирования и отладки JTools.

·

CD, содержащий базу BSD-файлов,

документацию и учебно-методи-ческие материалы, связанные с JTAG интерфейсом и

методом граничного сканирования.

Комплекс

реализует следующие функции:

·

Эмуляция загрузочных кабелей

фирм Altera (ByteBlaster MV), Xilinx (HW-DWNCBL-PC1), Atmel (ATDH2225);

·

Контроль сигналов на внешних

выводах БИС отлаживаемой системы;

·

Автоматический анализ реальной

схемы устройства;

·

Фиксирование состояния всех

контактов по возникновению заданной комбинации сигналов.

·

Режим полуавтоматической

отладки БИС и JTAG цепочки.

2.7 Комплекс средств

тестирования методом граничного сканирования (дополнительно)

Эмуляция

загрузочных кабелей Аппаратную

основу комплекса образует универсальный кабель, используемый для тестирования

методом граничного сканирования. Отличительной особенностью кабеля является

наличие программно управляемого режима эмуляции загрузочных кабелей различных

фирм производителей PLD.

Кабель

поддерживает режимы внутрисхемной эмуляции и внутрикристальной отладки, для

чего он имеет до 25 выводов управляющих сигналов и щупов для захвата событий.

Контроль

сигналов Программно-аппаратный

комплекс позволяет контролировать поведение проектов пользователя в реальных

системах путем вывода на экран ПЭВМ состояния внешних контактов БИС, входящих в

состав цепочки. Наблюдение не оказывает влияния на работу самой БИС. Более

того, в режиме тестирования возможно выборочное управление состоянием выводов

отдельных БИС (устанавливать уровень, отключать контакт от шины, генерировать

меандр), обеспечивая совмещение рабочих и тестовых режимов отлаживаемой

системы.

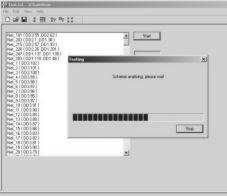

Автоматический

анализ схемы Программное

обеспечение позволяет произвести автоматический анализ схемы. Результат этого

анализа - составление списка межсоединений, выделение контактов, на которых

находиться константное значение, выделение контактов, значение на которых

противоречит ожидаемому.

Режим

полуавтоматической отладки БИС и JTAG цепочки Этот режим работы предназначен для анализа целостности JTAG

цепочки и работоспособности БИС, входящих в цепочку. Проверки соответствия

между реальной цепочкой и описанием, заданным пользователем. Предоставляться

средства отладки соединения между компьютером и платой тестируемого цифрового

устройства, а также JTAG цепочки на самой плате.

Фиксирование состояния всех контактов по возникновению заданной комбинации

сигналов Этот режим требует подключения дополнительных щупов универсального

кабеля к контрольным точкам. При возникновении на контрольных точках указанной

комбинации сигналов будет сделан мгновенный "снимок" состояния всех

контактов БИС, входящих в JTAG цепочку. После снимка программное обеспечение

забирает в ПЭВМ полученную информацию и предоставляет её для анализа

пользователю.

Заключение

В ходе работы было представлено описание отладочных средств

для МК семейства НС05, которое демонстрирует широкий диапазон их функциональных

возможностей и характеристик. Даже самые простые и доступные по цене МК

позволяют создать законченную разработку очень эффективную в работе.

Также в реферате были рассмотрены средства отладки БИС

на основе прототипных плат схем программируемой логики с интерфейсами ISA, PCI позволяющими отлаживать широкий спектр

пользовательских проектов, ориентированных на различные виды БИС.

Используемая литература:

1.

Микроконтроллер по цене

транзистора // Chip News — 1998. — № 11-12. — С. 16–19.

2.

Т. Ремизевич.

Микроконтроллеры семейства НС05 фирмы Motorola // Chip News. — 1998. — № 11-12.

— С. 22–26.

3.

Шагурин И.И. Архитектура и

функционирование микроконтроллеров семейства 68HC705 // Chip News. — 1999. — № 3.

— С. 2–10.

4.

Кобахидзе Ш. Нужны ли

профессионалу инструментальные средства? // Инженерная микроэлектроника. —

1998. — № 1. — С. 2–10.

5.

Буданов А. Средства

разработки и отладки программного обеспечения промышленных контроллеров на базе

8/16-разрядных микропроцессоров фирмы MOTOROLA // Инженерная микроэлектроника.

— № 1. — С. 32–35.