|

CS

|

OE

|

WR

|

A0. .10

|

D0. .7

|

Режим

|

|

M

|

X

|

X

|

Адрес

|

Дані

|

Зберігання

|

|

L

|

X

|

L

|

Запись

|

|

L

|

L

|

H

|

Зчитування

|

|

L

|

H

|

H

|

Заборона виходу

|

Технологічні та

електричні характеристики К537РУ10:

Технологія - КМОП

Організація - 2К×8

Час виборки, ns - не

більш 220

Напруга живлення,

V - 5

Струм живлення, мА

у режимі звернення

- 30

у режимі

зберігання - 1-2

Вхідна напруга, V

при логічному 0 -

min 0 - max 0,4

при логічній 1 -

min 0,9Ucc - max 0,5

Вихідна напруга, V

при логічному 0 -

min 0 - max 0,4

при логічній 1 -

min 2,4 - max 0,4

Вихід - 3 с.

Діапазон робочих

температур, ºС - - 10 - +70

Розрахуємо ПЗП:

Оскільки по

завданню необхідно створити ПЗП емкість 5К 8,

то було прийнято рішення використати дві схеми емкістю 2К

8,

то було прийнято рішення використати дві схеми емкістю 2К 8 та одну 1К

8 та одну 1К 8.

8.

Початкові дані для

мікросхеми КР556РТ20 1К 8:

8:

Кількість комірок

зовнішнього ПЗП NОЗУ - 1К×8

Вхідні струми:

при логічному 0, IIL

- 0,25 мА

при логічній 1, IIH

- 0,04 мА

Вхідна ємкість

логічних схем навантаження, СI - 5 пФ

Монтажні ємкості

усіх ланцюгов (См = 20 пФ).

Згідно завдання

кількість комірок ПЗП складає NОЗУ.

Розрядність ПЗП nОЗУ

повинна відповідати розрядності обробки даних ЦП.

Інформаційна

ємкість СОЗУ визначається по формулі:

Необхідна

швидкодія ПЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128

тривалість циклу запису (зчитування) tС равно 2ТМТ, де ТМТ

- тривалість машинного такту.

При частоті

кварцевого резонатора fтг = 9 МГц тривалість tС дорівнює:

Тривалість циклу

мікросхеми пам’яті tcy повинна задовольняти нерівності:

У якості

мікросхеми ПЗП виберемо КР556РТ20, тому що вона ідеально підходить і не створює

збитковості для даного випадку. Для даної мікросхеми пам’яті ємкість 1К, а

розрядність слова 8 біт:

.

.

Розрахуємо число

ВІС ПЗП в ряду матриці:

де nБИС

- розрядність обраної мікросхеми пам’яті.

Визначимо число

розрядів стовбців матриці:

де NБИС

- кількість комірок обраної мікросхеми пам’яті.

Загальна кількість

ВІС ПЗП дорівнює:

Таким чином,

кількість корпусів ПЗП дорівнює 1.

Визначимо стум

навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу

ВІС ПЗП по формулам:

IAL = m

* IIAL

= 1 * 0,25 = 0,25 мА

IAH = m

* IIAH

= 1 * 0,04 = 0,04 мА

CA = m * CIA + Cm

= 1 * 5 + 20 = 25 пФ

де IIАL,

IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу

обраної ВІС ПЗП. CIА - вхідна ємкість по входу адресу ВІС ПЗП.

Визначимо струми

навантаження ICSL, ICSH і величину ємкісного навантаження

СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL =

mp * IICSL = 1 * 0,25 = 0,25 мА

ICSH =

mp * IICSH = 1 * 0,04 = 0,04 мА

CCS = mp

* CICS

+ Cm = 1 * 5 + 20 = 25 пФ

де IICSL,

IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS)

ВІС ПЗП.

CСS -

вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ПЗП.

Враховуючи, що на

відміну від ОЗП інформація з ПЗП тільки зчитується, то необхідно визначити

струми навантаження і ємкість навантаження на інформаційні виходи ВІС ПЗП по

формулам:

IQL = mР

* IIL

= 1 * 0,25

= 0,25 мА

IQH = mР

* IIH

= 1 * 0,04

= 0,04 мА

CQ = mC

* CQO

+ mР *CI + Cm = 1 * 5 + 1 * 5 + 20 = 30 пФ

де IQL,

IQH - вхідні струми логічного 0 і логічної 1 мікросхем навантаження

ВІС ПЗП, CQO - вихідна ємкість одного інформаційного виходу ВІС ПЗП,

CI - вхідна ємкість мікросхем навантаження ВІС ПЗП.

Отримані значення

струмів не повинні перевищувати граничні значення для обраних мікросхем пам’яті.

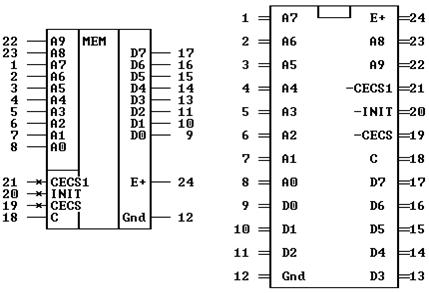

Рис.7 Умовно

графічне позначення ПЗП КР556РТ20

Найменування

виводів:

A0 ÷ A9 -

адресні входи.

D0 ÷ D7 -

шина даних вводу/виводу.

CECS, CECS1 -

вибір мікросхеми

Технологічні та

електричні характеристики КР556РТ20:

Технологія - ТТЛШ

Організація - 1К×8

Час виборки, ns - не

більш 65

Напруга живлення,

V - 5

Струм живлення, мА

- 180 мА

Вхідна напруга, V

при логічному 0 -

min 2,4 - max 0,5

при логічній 1 -

min 2,4 - max 0,5

Вихідна напруга, V

при логічному 0 -

min 2,4 - max 0,5

при логічній 1 -

min 2,4 - max 0,5

Вихід - 3 с.

Потужність

споживання, mW - 875

Діапазон робочих

температур, ºС - - 10 - +70

Початкові дані для

мікросхеми КР556РТ18 2К 8:

8:

Кількість комірок

зовнішнього ПЗП NОЗУ - 4К×8

Вхідні струми:

при логічному 0, IIL

- 0,25 мА

при логічній 1, IIH

- 0,04 мА

Вхідна ємкість

логічних схем навантаження, СI - 5 пФ

Монтажні ємкості

усіх ланцюгів (См = 20 пФ).

Згідно завдання

кількість комірок ПЗП складає NОЗУ.

Розрядність ПЗП nОЗУ

повинна відповідати розрядності обробки даних ЦП. Інформаційна ємкість СОЗУ

визначається по формулі:

Необхідна

швидкодія ПЗП визначається по тимчасовим діаграмам ЦП. Для МК ATmega128

тривалість циклу запису (зчитування) tС равно 2ТМТ, де ТМТ

- тривалість машинного такту. При частоті кварцевого резонатора fтг

= 9 МГц тривалість tС дорівнює:

Тривалість циклу

мікросхеми пам’яті tcy повинна задовольняти нерівності:

У якості

мікросхеми ПЗП виберемо КР556РТ20, тому що вона ідеально підходить і не створює

збитковості для даного випадку. Для даної мікросхеми пам’яті ємкість 1К, а

розрядність слова 8 біт:

.

.

Розрахуємо число

ВІС ПЗП в ряду матриці:

де nБИС

- розрядність обраної мікросхеми пам’яті. Визначимо число розрядів стовбців

матриці:

де NБИС

- кількість комірок обраної мікросхеми пам’яті.

Загальна кількість

ВІС ПЗП дорівнює:

Таким чином,

кількість корпусів ПЗП дорівнює 2.

Визначимо стум

навантаження і ємкістне навантаження для схем вводу адреси по ланцюгам адресу

ВІС ПЗП по формулам:

IAL = m

* IIAL

= 2 * 0,25 = 0,50 мА, IAH = m * IIAH = 2 * 0,04 = 0,08 мА

CA = m * CIA + Cm

= 2 * 5 + 20 = 30 пФ

де IIАL,

IIAH - вхідні токи логічного 0 і логічної 1 по ланцюгам адресу

обраної ВІС ПЗП.

CIА - вхідна

ємкість по входу адресу ВІС ПЗП.

Визначимо струми

навантаження ICSL, ICSH і величину ємкісного навантаження

СCS по ланцюгам вибору мікросхем (CS) по формулам:

ICSL =

mp * IICSL = 1 * 0,25 = 0,25 мА

ICSH =

mp * IICSH = 1 * 0,04 = 0,04 мА

CCS = mp

* CICS

+ Cm = 1 * 5 + 20 = 25 пФ

де IICSL,

IICSH - вхідні струми логічного 0 і логічної 1 по ланцюгам вибору (CS)

ВІС ПЗП.

CСS -

вхідна ємкість по ланцюгам вибору мікросхем (CS) ВІС ПЗП.

Враховуючи, що на

відміну від ОЗП інформація з ПЗП тільки зчитується, то необхідно визначити

струми навантаження і ємкість навантаження на інформаційні виходи ВІС ПЗП по

формулам:

IQL = mР

* IIL

= 1 * 0,25

= 0,25 мА

IQH = mР

* IIH

= 1 * 0,04

= 0,04 мА

CQ = mC

* CQO

+ mР *CI + Cm = 2 * 5 + 1 * 5 + 20 = 35 пФ

де IQL,

IQH - вхідні струми логічного 0 і логічної 1 мікросхем навантаження

ВІС ПЗП, CQO - вихідна ємкість одного інформаційного виходу ВІС ПЗП,

CI - вхідна ємкість мікросхем навантаження ВІС ПЗП.

Отримані значення

струмів не повинні перевищувати граничні значення для обраних мікросхем пам’яті.

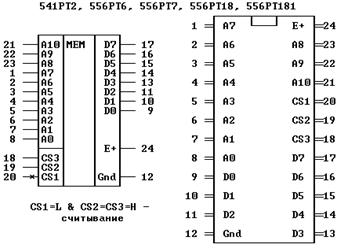

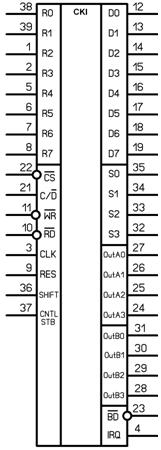

Рис.8 Умовно графічне

позначення ПЗП КР556РТ18

Найменування

виводів:

A0 ÷ A10 -

адресні входи.

D0 ÷ D7 -

шина даних вводу/виводу.

CS1 ÷ СS3 -

вибір мікросхеми

Технологічні та

електричні характеристики КР556РТ20:

Технологія - ТТЛШ

Організація - 2К×8

Час виборки, ns - не

більш 60

Напруга живлення,

V - 5

Струм живлення, мА

- 180 мА

Вхідна напруга, V

при логічному 0 -

min 2,4 - max 0,5

при логічній 1 -

min 2,4 - max 0,5

Вихідна напруга, V

при логічному 0 -

min 2,4 - max 0,5

при логічній 1 -

min 2,4 - max 0,5

Вихід - 3 с.

Потужність

споживання, mW - 875

Діапазон робочих

температур, ºС - - 10 - +70

Рис.9 - Схема

підключення процесорного блоку і пам’яті

2.3 Інтервальний таймер

Одним з елементів,

обумовлених завданням, є інтервальний таймер i8254. Таймер призначений для

формування затримок послідовності імпульсів, формування одиночних імпульсів

заданої тривалості, формування стробуємих імпульсів із програмованою затримкою.

Виконаний по n-МОП технології.

Рис.10 - Умовне

графічне позначення таймеру i8254

D0 - D7 - двонаправлена

шина даних з високоімпедансним станом.

А0 - А1 - розряди

шини даних, визначають регістр, що буде адресуватися: А1А0 = 00 - адреса каналу

0; А1А0 = 01 - адреса каналу 1; А1А0 = 10 - адреси каналу 2; А1А0 = 11 - адреса

регістра керуючого слова

- вибір кристала

- вибір кристала

- сигнал запису

- сигнал запису

- сигналу читання

- сигналу читання

CLK0 - CLK2 - вхід

дозволу подачі імпульсу від зовнішнього джерела

GATE0 - GATE2 - вхід

дозволу подачі імпульсу сlk на таймер/лічильник

OUT0 - OUT2 - вихід

таймерів/лічильників

Вхідні сигнали

CLK0 - CLK2 подаються через схеми із зовнішніми керуючими входами GATE0 - GATE2.

Кожен лічильник має вихідний сигнал OUT. Інші вузли схеми призначені для

установки режиму й реалізації інтерфейсу із системною шиною.

Для функціонування

таймера мікроконтролер повинен завантажити керуючі слова, значення яких

позначають режим кожного лічильника, і необхідні початкові значення. У завданні

нам дані параметри для програмування таймера, тому ми проініціализуємо його в

розділі розробки програм ініціалізації.

Електричні

параметри i8254:

1. Напруга

живлення - 5 В

2. Вихідна напруга:

високого рівня -

2,4 В

низькі рівні - 0,5

В

3. Вихідний струм

високого рівня - 1 мА

4. Вихідний струм

низького рівня - 5 мА

5. Вхідний струм

високого рівня - 30 мкА

6. Вхідний струм

низького рівня - 30 мкА

Рис.11 - Схема

підключення таймера i8254

Згідно із

завданням, у нашій МПС повинен бути використаний аналого-цифровий перетворювач.

Це пристрій, який перетворює аналоговий сигнал у цифровий код. Цей код повинен

потрапляти на всі пристрої, таким чином, АЦП підключається до загальної шини.

Варіантом

передбачено використання 12ти розрядного швидко-діючого АЦП послідовного

наближення, працюючого із ТТЛ-рівнями. Так як дана мікросхема не має окремого

блоку цифрового керування, то включення АЦП до шини даних проводиться завдяки

регістру К1810ИР82. Нижче наведено УГП MAX201В (іноземний аналог).

Рис.12 - Умовно

графічне позначення MAX201B

Основні електричні

параметри мікросхеми приведені нижче:

Напруга живлення: +5±10%В,

- 15±15%

Максимальний

вхідний струм лог.1: 100мкА

Максимальний

вхідний струм лог.0: 100мкА

Мінімальна вхідна

напруга лог.1: 2В

Максимальна вхідна

напруга лог.0: 0,8В

Максимальний

вихідний струм лог.1: 0,5мА

Максимальний

вихідний струм лог.0: 3,2мА

Мінімальна вихідна

напруга лог.1: 2,4В

Максимальна

вихідна напруга лог.0: 0,4В

Вхідна ємність по

всіх виводах (на частоті 1МГц): 6пФ

Вихідна ємність (на

частоті 1МГц): 5пФ

Похибка

перетворення: ±1/2ОМР

Час перетворення: 20мкС

Струм живлення: 15мА

Споживана

потужність: 800мВт

Для керування індикацією

та сканування клавіатури використовується спеціалізована мікросхема i8279. Вона

являє собою контролер клавіатури та індикації. Мікросхема має внутрішній ОЗП

клавіатури та індикації, може працювати у декількох режимах і дозволяє керувати

восьми - або шістнадцятирозрядною індикацією та опитувати до 128 клавіш або

дискретних датчиків. Умовне графічне позначення мікросхеми приведене на рис.14.

Рис.13-

Умовне-графічне позначення мікросхеми i8279

Внутрішня

адресація виробляється по входу A0, тому на цей вхід потрібно подати сигнал з

адресної шини. Обмін даними йде по шині даних. Входи RL0-RL7 мікросхеми служать

для зчитування стану клавіш клавіатури; виходи OutA3-OutA0, OutB0-OutB3 підключаються

до індикаторів; виходи S0-S3 - це виходи сканування рядків клавіатури й

перебору індикаторів при відображенні. При надходженні інформації від

клавіатури контролер виробляє запит на переривання, виставляючи на виході IRQ

сигнал активного рівня. Цей сигнал надходить на один із входів зовнішніх

переривань мікроконтролера.

Найменування

виводів мікросхеми i8279:

D0…D7 -

входи-виходи з третім станом

CS - вибір

мікросхеми

RD - читання

WR - запис

A0 або C/D -

команда / данні

CLK - синхронізація

RES - початкова

установа

S0…S3 - сканування

BD - гасіння

індикації

OUTA3… OUTA0,

OUTB3… OUTB0 - коди символів

R0…R7 - прийом

сигналів з клавіатури

SHIFT - верхній /

нижній регістр

IRQ - запит

переривання

Технологічні та

електричні характеристики:

Технологія - ТТЛШ

Вихідна напруга, В:

високого рівня -

2,4

низького рівня - 0.45

Вихідний струм, мA:

при напрузі

низького рівня - 5

при напрузі

високого рівня - 1

Вхідний струм, мкA:

низького рівня - 30

високого рівня - 30

Потужність - 350

мВт

Струм споживання -

60 мА

Режими роботи

інтерфейсу клавіатури:

1. Послідовне

опитування матриці клавіш із декодуванням і забороною уведення двох одночасно

натиснутих клавіш.

2. Послідовне

опитування з дешифруванням лічильника сканування з дозволом натискання N клавіш

(N<=8).

3. Послідовний

режим без дешифрації клавіш із забороною уведення 2х і більше натиснутих клавіш

(S0-S3 - Висновки лічильника, до нього підключений 8 розрядний дешифратор (128

кл))

4. Послідовне

опитування без дешифрування й з дозволом N натиснутих клавіш N<=8.

5. Послідовне

опитування матриці датчиків з дешифруванням матриці сканування.

6. Послідовне

опитування матриці датчиків без дешифрування матриці сканування.

7. Стробований

вхід з дешифруванням лічильника сканування, що використається для опитування.

8. Стробований

вхід без дешифрування лічильника сканування, що використається для опитування.

Режими роботи

блоку індикації:

0. Виводить символ

на 8мі розрядну індикацію, з розміщенням їх ліворуч праворуч.

1. Виводить символ

на 16ти розрядну індикацію, з розміщенням їх ліворуч праворуч.

2. Виводить символ

на 8мі розрядну індикацію, зі зрушенням раніше відображеної інформації вліво.

3. Виводить символ

на 16ти розрядну індикацію, зі зрушенням раніше відображеної інформації вліво.

Згідно завданню треба

організувати 8 індикаторів та 11 клавіш.

Для перетворення

двійкового коду у семисегментний використаємо дешифратор К155ИД7, який має три

входи і вісім виходів, чого достатньо для виконання поставленої задачі. Даний

дешифратор у своєму составі має керуючі входи для організації динамічної

індикації.

Рис.14 - Умовне

графічне позначення К155ИД7

Найменування

виводів:

А0-А2 - адресні

входи,

Q0-Q7 - лінії

виходу,

С1-С3 - ліній

вибору мікросхеми.

Технологічні та

електричні характеристики:

Технологія - ТТЛШ

Напруга живлення,

V - 5

Вихідна напруга, V

високого рівня -

2,2

низького рівня - 0.8

Вихідний струм, mA

при напрузі

високого рівня - 20

при напрузі

низького рівня - 8

Струм споживання,

mA – 74

Рис.15 - Схема

підключення блоку i8279

Сформуємо формат

команди встановлення режиму роботи контролера:

ICW1 = 00000001B =

01H

Обрано Режим 0

роботи інтерфейсу індикації та Режим 1 роботи інтерфейсу клавіатури, вивід

символів на 8мі розрядну індикацію з розміщенням їх ліворуч праворуч та з

запереченням натискання двох або більше клавіш.

Сформуємо формат

команди програмування синхронізації: ICW2 = 00110100B = 34H. Коефіцієнт

переліку вибрано рівним 20, тобто 10100В, тому що внутрішня частота інтерфейсу

не повинна перевищувати 100кГц (2МГц /20 = 100кГц).

Сформуємо формат

команди запису у ОЗП індикації:

ICW3 = 10010000B =

90H

Сформуємо формат

команди читання ОЗП клавіатури:

ICW4 = 01010000B =

50H

Програма ініціалізації

контролера клавіатури і індикації i8279

|

Мітка

|

Мнємокод

|

Операнди

|

Коментарії

|

i8279:

m1:

|

. equ

. equ

. equ

. equ

. equ

. equ

ldi

sts

ldi

sts

ldi

sts

ldi

ldi

mov

sts

dec

cpi

brne

ldi

lds

mov

ret

|

ICW1 = 0x01

ICW2 = 0x34

ICW3 = 0x90

ICW4 = 0x50

Adr2 = 0x8000

Adr1 = 0x8001

R0, ICW1

Adr1, R0

R0, ICW2

Adr1, R0

R0, ICW3

Adr1, R0

R1, 0x08

R2, 0x100

R3, R2

Adr2, R3

R2

R2, 0

m1

R4, 0x300

R5, Adr2

R4, R5

|

; команда установки режиму

; команда программ. синхронізації

; команда запису в ОЗП індикації

; команда читання ОЗП клавіатури

; адреса завантаження команд

; адреса завантаження даних

; завантаження команди режиму роботи

; у контролер

; завантаження команди програмування

; синхронізації у котролер

; завантаження команди запису в ОЗП

; індикації у контролер

; завантаження лічильника

; завантаження початкової адреси

; завантаження даних в ОЗП індикації

; декремент регістру

; порівняння значення в регістрі з 0

; перехід на мітку, якщо не рівно 0

; завантаження початкової адреси

; читання ОЗП клавіатури

; зміст регістру R5 відправити у пам’ять по адресу,

який знаходиться в R4

|

Адаптер

послідовного інтерфейсу слугує для обміну інформацією у послідовному коді у

двох режимах: асинхронному та синхронному.

Умовно графічне

зображення адаптеру наведено на Рис.16

Рис.16 - Адаптер

послідовного інтерфейсу i8254

Електричні

параметри i8251:

1. Напруга

живлення - 5 В

2. Вихідна напруга:

високого рівня -

2,4 В

низькі рівні -

0,45 В

3. Вихідний струм

високого рівня - 1 мА

4. Вихідний струм

низького рівня - 5 мА

5. Вхідний струм

високого рівня - 30 мкА

6. Вхідний струм

низького рівня - 30 мкА

Програмування

адаптеру послідовного інтерфейсу Intel 8251

Завдання: Запрограмувати

адаптер i8251 для роботи у асинхронному режимі на випадок:

кількість стоп-біт:

2

кількість

інформаційних біт: 8

контроль парності

коеф. ділення

частоти синхронізації: 16

кількість посилок:

48

Програма:

Спочатку сформуємо

слово приказу - 11011110 #DEH

Початковий адрес у

пам’яті #100Н

Кінцевий адрес у

пам’яті #130Н

Адреса адаптеру #E000H

i8251: ; оголошення

констант

. equadr1 = 0xE001;

адреса А0=1

. equadr2 = 0xE000;

адреса адаптеру

. equmask1 = 0x01;

відокремлення TxRDY

. equmask2 = 0x02;

відокремлення RxRDY

. equmask3 =

0b00111000; виявлення помилок

ldiR0, 0xDE; слово

приказу

stsadr1, R0; програмув.

на асинхр. режим

m1: ldiR0, 0x01; завантаження

РПД=1

stsadr1, R0; слово

команда, дозвіл

; передачі

m2: ldsR0, adr1; читання

слова-стану

andiR0, mask1; маскування

біта TxRDY

breqm2

ldiR31, 0x01; поч.

адреса для видачі 100H потрапляє у

; старший байт Z (ZH=R31)

ldiR2, 0x30; 48

посилок

m3: ; програмув. передачі

ld R3, Z+; передача

із слідуючої комірки у РОН

stsadr2, R3; видача

байту інформації

decR2; декримент

лічильника

cpiR2, 0

brnem3

RET

m4: ldiR0, 0x04; завантаження

РПД=1

stsadr1, R0; слово

команда, дозвіл

; прийому

m5: ldsR0, adr1; читання

слова-стану

andiR0, mask2; маскування

біта RxRDY

breqm5

ldsR0, adr1; читання

слова-стану

andiR0, mask3; перевірка

на факт помилки

brneerror

ldiR30, 0x31; поч.

адреса для прийому 131H

; потрапляє

побайтово до молодшого та

; старшого байтів

рег. Z (ZL=R30)

ldiR31, 0x01; (ZH=R31)

ldiR2, 0x30; 48

посилок

m6: ; програмув. прийому

ldsR3, adr2; прийом

байту інформації

stZ+, R3; прийом у

слідуючу комірку РОН

decR2; декримент

лічильника

cpiR2, 0

brnem6

RET

2.7 Розрахунок електричних навантажень на лінії мікросхем

Проведемо розрахунок

навантажувальних характеристик для виходів мікроконтролера для шини даних,

адреси і керування.

Навантаження на

шину даних мікроконтролера визначається по формулі:

IвихDL

=IвхСKI + IвхPIТ + IвхOZU + IвхPZU

+ IвхACP = 0,03 + 0,03 + 1,6 + 0,25 + 0,1 = = 2,01 мА;

IвихDH

= IвхCKI + IвхPIТ + IвхOZU + IвхPZU

+IвхACP = 0,03 + 0,03 + 0,1 + 0,04 + 0,1 = = 0,3 мА;

СD = СCKI

+ СPIТ + СOZU + СPZU + СACP = 5 + 5

+ 25 + 35 + 6 = 76 пФ.

Так як

навантаження на шину даних не перевищує 40 мА, то використання додаткового

шиного формувача не потрібне. Використаний буферний регістр відповідає

поставленим вимогам.

Навантаження на

шину адреси мікроконтролера визначається по формулі:

IвихАL

=IвхСKI + IвхPIТ + IвхOZU + IвхPZU

= 0,03 + 0,03 + 1,6 + 0,50 = 2,16 мА;

IвихАH

= IвхCKI + IвхPIТ + IвхOZU + IвхPZU

= 0,03 + 0,03 + 0,1 + 0,08 = 0,24 мА;

СА = СCKI

+ СPIТ + СOZU + СPZU = 5 + 5 + 25 + 30 = 65 пФ.

Так як

навантаження на шину адреси не перевищує 40 мА, то використання додаткового

шиного формувача не потрібне. Використаний буферний регістр відповідає

поставленим вимогам.

Навантаження на

шину керування мікроконтролера визначається по формулі:

IвихСL

=IвхСKI + IвхPIТ + IвхOZU + IвхPZU

= 0,03 + 0,03 + 1,6 + 0,25 = 1,94 мА;

IвихСH

= IвхCKI + IвхPIТ + IвхOZU + IвхPZU

= 0,03 + 0,03 + 0,1 + 0,04 = 0,23 мА;

СС = СCKI

+ СPIТ + СOZU + СPZU = 5 + 5 + 25 + 25 = 60 пФ.

Отримані при

розрахунку значення струмув та ємностей не перевищують граничні значення.

В ході виконання

курсової роботи була розроблена повна принципова схема мікропроцесорної системи.

Були розглянуті різні варіанти структурної та принципової схем. Згідно із

завданням складена програма ініціалізації окремих блоків. Обрані та розраховані

необхідні у системі елементи. Була розглянута видача і запис інформації в

пам’ять, АЦП, керування системою за допомогою клавіатури та індикації.

Виконання курсової

дозволить у подальшому без труднощів розробляти подібні та ще більш складні

процесорні системи.