Развитие технологии МОП ИС

Содержание

Стр.

Введение. 3

1 Развитие МОП ИС. 4

2 Принцип работы и

структура МОП - транзистора. 6

3 Технология n – канальных МОП СБИС. 8

3.1 Исходный

материал. 10

3.2 Изоляция. 11

3.3

Легирование области канала. 12

3.4

Формирование затвора. 13

3.5

Формирование областей истока и стока. 14

3.6

Нанесение и оплавление фосфорно-силикатного стекла (ФСС) 15

3.7

Металлизация. 16

4 Особенности технологии КМОП БИС.. 17

5 Особенности субмикронных МОП – транзисторов. 21

5.1

Конструкции МОП - транзисторов в СБИС.. 23

5.2 Методы

улучшения характеристик МОП - транзисторов. 26

Список использованных

источников. 31

Введение

Схемы

на МОП (металл - окисел - полупроводник) - транзисторах составляют в настоящее

время значительную часть изделий, выпускаемых электронной промышленностью.

На их основе строится большинство интегральных схем с сверх большой (СБИС) и большой степенью

интеграции. Схемы на МОП - транзисторах

занимают доминирующее положение при

создании таких функционально законченных изделий, как постоянные и оперативные запоминающие

устройства, микроконтроллеры, микропроцессоры,

АЦП, ЦАП и т.д.

Благодаря своей высокой надежности и

большой функциональной сложности МОП СБИС позволяют строить более дешевую аппаратуру. При равной

функциональной сложности они имеют меньшие

геометрические размеры, чем схемы на биполярных транзисторах, а процесс

их изготовления, как правило, проще, чем

технология схем на биполярных приборах. Значительным достоинством МОП ИС

является и то, что их применение в устройствах позволяет повысить надежность и сложность последних, а также

предсказывать параметры разрабатываемых на их основе систем [1].

Развитие технологии изготовления МОП ИС

позволило повысить скорость работы цифровых микросхем, которые в настоящее

время строятся на МОП транзисторах и уменьшить при этом габаритные размеры

микросхем.

В работе рассматриваются основные этапы

технологии, используемые при изготовлении МОП – транзисторов и тенденция

развития технологии.

1 Развитие МОП ИС

Принцип работы полевого транзистора (МОП -

транзистора) был известен ещё до появления биполярного транзистора. Однако лишь

недавно, благодаря достижению стабильности и контролируемости технологического

процесса МОП БИС стали реальностью.

Согласно литературным источникам, первые попытки

построить активный полупроводниковый прибор, основанный на эффекте поля, были

предприняты Лилиефельдом в начале 30 – х гг. О. Хейл запатентовал свое

открытие в Великобритании в 1935 г. Первая действующая модель униполярного

полевого транзистора была разработана фирмой Bell Telephone Laboratories, где в 1948 г. Бардиным и Бреттейном был открыт транзисторный эффект. Ученые наблюдали этот эффект в серии

экспериментов по модуляции тока, протекающего через точечные контакты с

кристаллом германия. Их открытие проложило дорогу к разработке точечных

транзисторов и к изобретению биполярных транзисторов, работа которых в большей

степени основаны на инжекции неосновных носителей заряда, чем на полевом

эффекте. Затем внимание исследователей переключилось на эти два типа

биполярных транзисторов, и развитие полевых транзисторов фактически

приостановилось.

В 1952 г. Шокли описал полевой транзистор с управляющим

обратно смещенным р - n - переходом. Такие полевые транзисторы были впоследствии

изготовлены и исследованы Декеем и Россом, которые в 1955 г. аналитически определили предельные параметры подобных транзисторов. Однако первые попытки

изготовить полевой МОП - транзистор оказались безуспешными, поскольку не

удавалось получить контролируемую и стабильную поверхность.

В 1958 г. появилась первая монолитная ИС с биполярными

плоскостными транзисторами.

Важным достижением в полупроводниковой технике явилась

разработка в начале 60-х гг. кремниевой планарной технологии. Выращивание,

травление и повторное выращивание изолирующего слоя окисла на поверхности

кремниевой подложки позволили получить значительно более стабильную

поверхность, а также контролировать геометрические размеры с большей точностью,

чем это было возможно ранее. В результате наступил период в развитии МОП - транзисторов,

когда стало возможным заменить ими электронные лампы и дорогостоящие

биполярные транзисторы. Попытки серийного производства МОП - транзисторов

натолкнулись на трудности, связанные с миграцией заряда вдоль поверхности,

которая приводила к ухудшению их электрических характеристик. С последующим

улучшением технологии появились первые надежные дискретные МОП -транзисторы с

воспроизводимыми параметрами.

ИС содержащая меньше 100 полевых транзисторов была

изготовлена в 1961 г Bell Laboratories более чем через 30 лет после

открытия принципа действия полевого транзистора.

Проблемы контроля технологического процесса

постоянно беспокоили изготовителей МОП – схем вплоть до 1967 г. В это время процент годных МОП – схем со стабильными параметрами был увеличен как за счёт усовершенствования

основного МОП процесса, так и за счёт усиления технологической дисциплины и

установления строго контролируемой окружающей среды в чистых помещениях на

критических этапах технологического процесса. Впоследствии процент входа годной

продукции продолжал непрерывно расти благодаря накоплению производственного

опыта и созданию лучших оборудования, инструментов и исходных материалов.

В дополнение к повышению качества материалов и

оборудования значительно возрос и объем знаний в области физики поверхности

полупроводников, что привело к усовершенствованию технологического процесса в

некоторых его критических точках. Другим фактором, который помог

увеличить выход годной продукции, было развитие схемотехники, позволившее полнее

использовать специфические свойства МОП – транзисторов [1].

В 1969 году ИС на МОП транзисторах

содержали от 1000 до 10000 транзисторов. 1971 году была придумана технология

ионной имплантации, 1975 году благодаря технологии с самосовмещённого затвора,

стало возможным производство СБИС (10000 – 100000 транзисторов).

В 1980 году – степень интеграции

увеличилась до 100 000 транзисторов и больше на кристалле, и появились

УБИС (ультра большие ИС).

Наконец, с 1990 годов производятся ИС с

1000000 и больше транзисторов. Благодаря развитию технологии одна микросхема

малых размеров может выполнять множество функций и с большой

производительностью.

2 Принцип работы

и структура МОП - транзистора

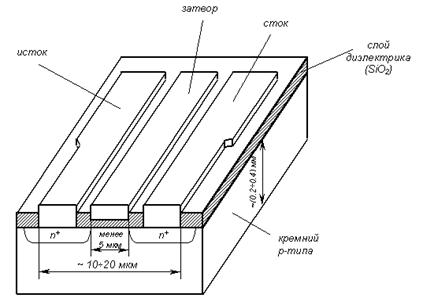

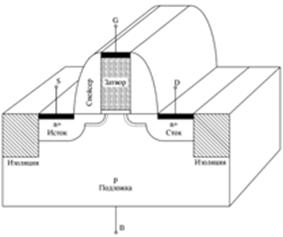

Структура n-канального МОП

- транзистора приведена на рис. 2.1. Затвор выполнен на металле, а сток и исток

- на n-областях (при замене на p-области

получается p-канальный транзистор). Области n(p) называют

диффузионными. При подаче напряжений на затвор и сток (исток) под затвором

образуется тонкий канал, по которому течет ток, создаваемый движением

электронов (дырок) от истока к стоку в nМОП (pМОП) -

транзисторе. Толщина канала составляет около 100 ангстрем. Поскольку

подвижность электронов почти в 2,5 раза выше, чем подвижность дырок,

проводимость открытого n МОП - транзистора

в 2,5 раза больше проводимости p МОП - транзистора.

МОП - транзисторы имеют следующие усредненные характеристики: входной ток - 5

мкА, входное сопротивление в статическом режиме - 106 Ом, сопротивление исток -

сток закрытого транзистора 1012 Ом, сопротивление открытого транзистора - сотни

Ом, паразитная емкость исток - сток - 10 пФ. В биполярном транзисторе движение

носителей происходит в слое, имеющем значительно большую толщину, чем в

канальном транзисторе. Биполярные транзисторы имеют следующие усредненные

характеристики: входной ток - 1 мкА, входное сопротивление - сотни Ом,

сопротивление открытого транзистора - десятки Ом, сопротивление закрытого

транзистора - сотни кОм, паразитная емкость эмиттер - коллектор - 10 пФ.

Рисунок – 2.1 - Структура

n-канального МОП – транзистора

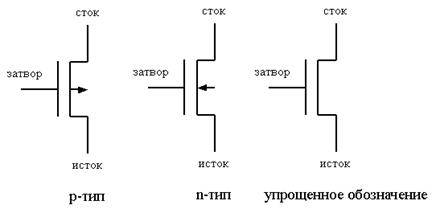

На рис. 2.2 показаны стандартные обозначения

n МОП- и p МОП - транзисторов.

Рисунок 2.2 - Обозначения n МОП- и p МОП – транзисторов

3 Технология n – канальных

МОП СБИС

Полевой транзистор на основе структуры

металл – окисел – полупроводник (МОП ПТ) наиболее широко используется в СБИС.

До начала 70 – х гг. доминировали интегральные схемы на основе p – канальных

МОП ПТ, что было связано с низким качеством окисла и границы раздела SiO2/Si. В результате

возникали заряды, приводящие к инверсии типа проводимости на поверхности

подложки p – типа. После 70 – х гг. доминируют n – канальные

МОП ИС, преимущество которых проявляется в более высокой подвижности электронов

по сравнению с дырками, и, следовательно, в большем быстродействии ИС.

С технологической точки зрения изготовление

МОП – транзисторов значительно проще биполярных транзисторов. Это можно видеть

из сравнительного анализа данных таблицы 3.1.

Таблица 3.1 –

Сравнение ключевых процессов и условий технологии производства биполярных и МОП

– интегральных схем.

|

Биполярная

технология

|

МОП

- технология

|

|

4-7

процессов легирования (имплантация и/или диффузия)

Необходимость

полной изоляции элементов (изолированных островков)

Эпитаксиальный

процесс является одной из основных операций

Используется

от 6 до 8 фотолитографий

Более

100 технологических операций

10

процессов с температурой около (или выше) 1000 C

Коэффициент

передачи транзистора зависит от режимов легирования и термообработки

|

1-3

процесса легирования (имплантация, диффузия)

К

изоляции предъявляются менее жёсткие требования

Эпитаксиальный

процесс не обязателен

Используется

4 - 6 фотолитографий

Около

30 технологических операций

2

процесса с температурой около (или выше) 1000 C

Коэффициент

передачи транзистора существенно не зависит от режимов легирования

|

МОП

- транзистор имеет малую площадь и, обладая высоким входным сопротивлением,

потребляет малую мощность от источника сигнала. В дополнение, при нулевом

напряжении на затворе МОП ПТ с индуцированным каналом ток стока практически

отсутствует, т. е. мощность потребляется транзистором только во время подачи

напряжения на затвор. Процесс изготовления МОП - интегральных схем сводится к

формированию МОП – транзисторов и соединений между ними, поскольку МОП - структуры

могут использоваться не только в качестве транзисторов, но и как резисторы и

конденсаторы, т. е. практически все схемные функции можно реализовать на одних

МОП - структурах.

Рисунок 3.1 - Схема изготовления МОП ИМ с самосовмещенными

поликремниевыми затворами;

а — выращивание маскирующего оксида и первая фотолитография; б

— выращивание подзатворного оксида; в — наращивание

поликристаллического кремния; г — вторая фотолитография; д — диффузия

областей истоков и стоков;

е — осаждение плевки оксида; ж — третья фотолитография,

формирование металлизации

Благодаря

вышеуказанным факторам, МОП - интегральные схемы заняли ведущее положение в

области цифровой обработки информации. Рассмотрим типичный технологический

процесс изготовления МОП – транзистора с LOCOS-изоляцией. На рисунке

3.1 представлены основные этапы технологического процесса, а в разделах 3.1 –

3.7 более подробное их описание.

3.1 Исходный материал

Исходный материал - подложки слаболегированного

(порядка  ) кремния р - типа с ориентацией

поверхности вдоль (001) плоскости. Выбор подложек с ориентацией (001)

обусловлен значительно меньшей (на порядок) плотностью поверхностных состояний

по сравнению с ориентацией (111). При выборе уровня легирования подложки

принимают во внимание следующие обстоятельства. Чем слабее легирована подложка,

тем менее чувствительно пороговое напряжение транзистора к смещению на

подложке и тем меньшая емкость возникает между областями истока, стока и

подложкой. Однако если подложка легирована слишком слабо, обедненные области

истока и стока могут соприкасаться, приводя к проколам транзисторов. В дополнение,

слаболегированные подложки имеют высокую концентрацию неосновных носителей

заряда, что увеличивает токи утечки p-n-переходов при их обратном смещении. Эту проблему можно решить

двумя способами. Один из них заключается в выращивании слаболегированных (~

) кремния р - типа с ориентацией

поверхности вдоль (001) плоскости. Выбор подложек с ориентацией (001)

обусловлен значительно меньшей (на порядок) плотностью поверхностных состояний

по сравнению с ориентацией (111). При выборе уровня легирования подложки

принимают во внимание следующие обстоятельства. Чем слабее легирована подложка,

тем менее чувствительно пороговое напряжение транзистора к смещению на

подложке и тем меньшая емкость возникает между областями истока, стока и

подложкой. Однако если подложка легирована слишком слабо, обедненные области

истока и стока могут соприкасаться, приводя к проколам транзисторов. В дополнение,

слаболегированные подложки имеют высокую концентрацию неосновных носителей

заряда, что увеличивает токи утечки p-n-переходов при их обратном смещении. Эту проблему можно решить

двумя способами. Один из них заключается в выращивании слаболегированных (~ ) эпитаксиальных слоев р – типа на

сильнолегированных подложках р - типа (~

) эпитаксиальных слоев р – типа на

сильнолегированных подложках р - типа (~ ). Сильнолегированные

подложки имеют низкую концентрацию неосновных носителей заряда (электронов),

поэтому диффузионный ток в обратно смещенных переходах подавляется несмотря на

большую диффузионную длину неосновных носителей в эпитаксиальном слое. Второй

подход к решению проблемы основан на использовании эффекта внутреннего

гетерирования. На глубине подложки формируют преципитаты Si02, которые

существенно снижают время жизни неосновных носителей заряда при одновременной

очистке приповерхностных областей подложки.

). Сильнолегированные

подложки имеют низкую концентрацию неосновных носителей заряда (электронов),

поэтому диффузионный ток в обратно смещенных переходах подавляется несмотря на

большую диффузионную длину неосновных носителей в эпитаксиальном слое. Второй

подход к решению проблемы основан на использовании эффекта внутреннего

гетерирования. На глубине подложки формируют преципитаты Si02, которые

существенно снижают время жизни неосновных носителей заряда при одновременной

очистке приповерхностных областей подложки.

При переходе к высокой степени интеграции СБИС

особую роль приобретает изоляция отдельных активных транзисторов для подавления

паразитных электрических связей. На рисунке 3.2 показаны два смежных n - канальных МОП ПТ. Направление

проводимости активных транзисторов перпендикулярно поликремневому затвору. Однако

под затвором между соседними транзисторами могут возникать паразитные

транзисторы, как это показано на рисунке 3.1.

Рисунок 3.2 – Топология смежных n – канальных МОП ИТ с

общим поликремневым затвором, демонстрирующая появление паразитных

транзисторов:

а – вид сверху, на котором отмечены как

активный, так и паразитные транзисторы;

б – поперечное сечение по A-A соответствует структуре

с LCMOS – изоляцией. Области p+, проникающие в

подложку, ограничивают распространение канала и препятствуют формированию

паразитных транзисторов.

Для того чтобы устранить возможность появления

проводимости между соседними транзисторами, пороговое напряжение паразитных транзисторов

должно быть очень высоким. Это достигается путем формирования толстого

заглубленного слоя окисла между активными транзисторами. При

формировании МОП ПТ используют LOCMOS – изоляцию, основанную на локальном окислении

предварительно протравленных участков кремния.

Процесс локального окисления аналогичен процессу,

используемому для изоляции биполярных транзисторов, за исключением того, что

при изоляции МОП ПТ локальный окисел не должен пронизывать всю толщину

эпитаксиального слоя. Наряду с хорошими изолирующими свойствами, достоинством LOCOS-метода является преимущественное

заглубление окисла в подложку, так что поверхность остается почти плоской (это

важно при проведении процессов фотолитографии). В дополнение, для более

эффективной изоляции методом LOCOS можно формировать области, ограничивающие

распространение инверсного канала (рис. 3.2). Доза имплантации при легировании

ограничительных областей обычно составляет  ;

энергия имплантации выбирается достаточной для глубокого проникновения примеси

с учетом частичного окисления слоя.

;

энергия имплантации выбирается достаточной для глубокого проникновения примеси

с учетом частичного окисления слоя.

3.3 Легирование области

канала

Обычно проводится для регулировки величины

порогового напряжения МОП ПТ. В зависимости от режима работы транзистора

имплантируют ионы бора или фосфора. Для получения транзисторов, работающих в

режиме обеднения, имплантируют ионы фосфора (n-канал), для режима

обогащения - ионы бора (р - канал). Имплантацию проводят через тонкий слой

окисла (рис. 3.3). Дозу и энергию имплантации выбирают, исходя из требуемой

величины порогового напряжения с учетом толщины окисла. В связи с тенденцией

уменьшения длины канала в технологии СБИС применяют более глубокую имплантацию ионов

с большей дозой (или двухстадийную имплантацию с различными дозами и

энергиями): это позволяет избежать перекрытия обедненных исток - стоковых областей.

Рисунок 3.3 – Легирование области канала

для регулировки величины порогового напряжения МОП ПТ

Вместе с тем увеличение концентрации примеси в

области канала приводит и к нежелательным последствиям, т. к. сопровождается уменьшением

подвижности носителей заряда.

3.4 Формирование затвора

Производят путем осаждения поликристаллического

кремния (поли-Si) в соответствующую область транзистора, при этом при осаждении

поли-Si легируют фосфором до высокой концентрации носителей. Выбор поли – Si обусловлен его способностью

хорошо выдерживать высокотемпературную термообработку, а также одинаковой

величиной работы выхода, что упрощает регулировку пороговых напряжений МОП ПТ.

Вместе с тем сопротивление поли Si (>10 Ом) достаточно велико, что может

приводить к значительной задержке сигнала, проходящего по таким шинам, особенно

при большой их длине (например, общая шина для большого количества МОП –

транзисторов). Поэтому в последнее время формируют многослойные затворы с применением

слоёв силицидов тугоплавких металлов (рис. 3.4). Многослойный полицидный затвор

имеет низкое слоевое сопротивление при сохранении электронных свойств границы

раздела поли Si – SiO2. Области истока и стока формируют высокодозной имплантацией

ионов As в условиях их самосовмещения с каналом; при этом слои LOCOS – изоляции и затвора

играют роль маскирующего покрытия, которое обеспечивает локальность легирования.

Рисунок 3.4 – Формирование двухслойного

затвора и исток – стоковых областей МОП – полевого транзистора

К преимуществам метода, при котором используется

нанесение силицидов на поверхность легированного поли – Si (такая структура

называется полицид), относится снижение поверхностного сопротивления до 1-3  при сохранении хорошо изученной границы

раздела поли Si – SiO2.

при сохранении хорошо изученной границы

раздела поли Si – SiO2.

3.5 Формирование

областей истока и стока.

Для создания исток - стоковых областей более

других подходит мышьяк, который позволяет получать мелкие p-n-переходы с минимальной

диффузией в горизонтальном направлении. Доза имплантируемой примеси обычно достаточно

высока и лежит в диапазоне  , что обеспечивает

формирование низкоомных областей истока и стока. Энергия имплантируемых ионов

должна быть достаточно высокой, чтобы они смогли проникнуть через пленку подзатворного

окисла (см. рис. 3.4), но в то же время достаточно низкой для предотвращения их

проникновения через пленку поликремния и области локального окисления. Формируемые

таким образом области истока и стока самосовмещаются с затвором. Такое

самосовмещение способствует минимизации перекрытия затвора с областями истока

и стока, из которых примесь диффундирует в поперечном направлении. Тем самым

обеспечивается снижение емкостей связи. После легирования областей истока и

стока проводят отжиг имплантационных дефектов, для которого используют

окисляющую среду. При этом, наряду с отжигом дефектов и электрической

активацией примеси, происходит рост термического окисла, в том числе на поверхности

и боковых стенках поликремневого затвора. Слой окисла служит для электрической

изоляции исток -стоковых областей от затвора, а также для защиты областей

истока и стока от проникновения фосфора из осаждаемого на

последующих стадиях фосфорно - силикатного стекла.

, что обеспечивает

формирование низкоомных областей истока и стока. Энергия имплантируемых ионов

должна быть достаточно высокой, чтобы они смогли проникнуть через пленку подзатворного

окисла (см. рис. 3.4), но в то же время достаточно низкой для предотвращения их

проникновения через пленку поликремния и области локального окисления. Формируемые

таким образом области истока и стока самосовмещаются с затвором. Такое

самосовмещение способствует минимизации перекрытия затвора с областями истока

и стока, из которых примесь диффундирует в поперечном направлении. Тем самым

обеспечивается снижение емкостей связи. После легирования областей истока и

стока проводят отжиг имплантационных дефектов, для которого используют

окисляющую среду. При этом, наряду с отжигом дефектов и электрической

активацией примеси, происходит рост термического окисла, в том числе на поверхности

и боковых стенках поликремневого затвора. Слой окисла служит для электрической

изоляции исток -стоковых областей от затвора, а также для защиты областей

истока и стока от проникновения фосфора из осаждаемого на

последующих стадиях фосфорно - силикатного стекла.

3.6 Нанесение и

оплавление фосфорно-силикатного стекла (ФСС)

Слой ФСС получают осаждением окисла из парогазовой

смеси (методом CVD или LPCVD) с одновременным легированием фосфором до концентрации 6-8 ат %.

При таких концентрациях фосфора окисел приобретает свойство размягчаться вплоть

до оплавления при его нагреве до температуры 1000-1100 °С (при меньшей

концентрации процесс растекания затруднен, а концентрация фосфора выше 8 ат %

может вызвать коррозию алюминиевой металлизации кислотными продуктами реакции

фосфора с атмосферной влагой).

В интегральных схемах фосфорно-силикатное стекло

выполняет несколько функций. Фосфор в таком стекле защищает лежащую под ним

структуру прибора от подвижных ионов (Na+) и, кроме того, он делает стекло вязким,

облегчая его оплавление при повышенной температуре (этот высокотемпературный

процесс может быть также использован для дополнительного активирования и

разгонки примеси, имплантированной в области истока и стока). Оплавление

фосфорно силикатного стекла сглаживает рельеф, что улучшает воспроизведение

ступенчатого рельефа при его покрытии металлической плёнкой и способствует

облегчению формирования топологического рисунка слоя металлизации. Наконец,

слой ФСС изолирует металлический слой от поликремниевых шин.

Для создания контакта между ними в слое ФСС

вскрывают окна, после чего для сглаживания крутых боковых стенок окон проводят

повторное оплавление ФСС: такие структуры пригодны для нанесения металлизации.

3.7 Металлизация

На последнем этапе проводят осаждение металлического

слоя для изготовления контактов к областям истока, стока и затвора, а также

межэлементных проводящих соединений внутри интегральных схем. При этом контакт

к слою поликристаллического кремния обычно выполняют вне активных областей

транзистора. Это связано с тем, что за счёт быстрой диффузии алюминия через

слой поликристаллического кремния (диффузия по границам зёрен, усиленная

электрическим полем в области контакта) атомы алюминия могут достигать слоя

подзатворного диэлектрика и приводить к частичному раскислению SiO2. Слой подзатворного

диэлектрика делают обычно тонким, поэтому даже небольшое его повреждение

приводит к существенному изменению характеристик МОП – полевых транзисторов,

вплоть до их полного повреждения.

Для металлизации используют преимущественно

алюминий (чистый или в сочетании с другими металлами – например, добавление

меди в алюминий уменьшает вероятность электромиграции и связанных с этим

эффектом обрывов металлических дорожек). Существенное уменьшение контактного

сопротивление может быть достигнуто применением плёнок платины или вольфрама. В

частности, при отжиге структуры плёнка платины – кремний (поликремний)

формируется слой силицида платины, который позволяет снижать поверхностное

сопротивление областей истока, стока и затвора с 50 до 3  , что является особенно важным для СБИС

с высокой степенью интеграции. Последним на поверхность подложки осаждают

сплошной слой плазмохимического нитрида кремния (SiN), который герметизирует

подложку и предохраняет её от загрязнений и механических повреждений. В тех

местах, где необходимо сделать внешние (проволочные) выводы к слою

металлизации, в защитном покрытии встраивают контактные окна [2].

, что является особенно важным для СБИС

с высокой степенью интеграции. Последним на поверхность подложки осаждают

сплошной слой плазмохимического нитрида кремния (SiN), который герметизирует

подложку и предохраняет её от загрязнений и механических повреждений. В тех

местах, где необходимо сделать внешние (проволочные) выводы к слою

металлизации, в защитном покрытии встраивают контактные окна [2].

4 Особенности технологии

КМОП БИС

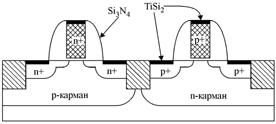

Технология комплементарных МОП - структур (КМОП)

является в настоящее время одной из самых распространенных технологий

СБИС. Технология КМОП заключается в формировании n- и р - канальных МОП - транзисторов

в одном кристалле и по сравнению с n-канальными МОП ИС они потребляют значительно

меньшую мощность. Особенностью технологии КМОП ИС является формирование на

пластине кремния больших областей с типом проводимости, отличающимся от типа

проводимости подложки. Такие области с другим типом проводимости называются

карманами. В настоящее время существуют технологии с р - карманами (на

пластинах n-типа

проводимости), с n-карманами (на пластинах р - типа) и с n-и р - карманами (на

почти компенсированном кремнии); примеры таких КМОП-структур приведены на рисунке

4.1. Недостатком интегральных схем с одним карманом является необходимость

перекомпенсации, т. е. введения примеси с противоположным типом проводимости в

концентрации, позволяющей изменить тип проводимости кремния. Для уверенной перекомпенсации

и, следовательно, малого разброса параметров по пластине, концентрация примеси

в кармане должна быть в 5-10 раз выше, чем в основной пластине. Как следствие,

возникают нежелательные эффекты (увеличение обратного смещения, увеличение

емкости между областями истока-стока и карманом). Технология с двумя отдельными

карманами (рисунок 4.1 в) свободна от этих недостатков, однако требует подложек

кремния с очень низким уровнем легирования n - Si ( -типа)

или p -

Si (

-типа)

или p -

Si ( -типа).

В этих случаях, возможно, получать профили и уровни легирования в каждом

кармане независимо. За исключением процедуры изготовления карманов, а также

некоторых особенностей регулировки пороговых напряжений, синтеза изоляции и активных

областей, при формировании КМОП СБИС используются те же технологические

процессы (в сходных технологических режимах), как и в случае n-МОП.

-типа).

В этих случаях, возможно, получать профили и уровни легирования в каждом

кармане независимо. За исключением процедуры изготовления карманов, а также

некоторых особенностей регулировки пороговых напряжений, синтеза изоляции и активных

областей, при формировании КМОП СБИС используются те же технологические

процессы (в сходных технологических режимах), как и в случае n-МОП.

Рисунок 4.1 – КМОП-структуры с p- каналом (а), n – каналом (б), двойным карманом (в)

На рисунке 4.2 показаны этапы технологии изготовления КМОП

структур. Далее описаны более подробно каждый из этапов.

1.

Исходный материал - слаболегированный эпитаксиальный слой  - типа, выращенный на сильнолегированной

n+ - подложке. Такая структура

в сочетании с соответствующим методом формирования элементов позволяет избежать

так называемого эффекта защелкивания (тиристорного эффекта).

- типа, выращенный на сильнолегированной

n+ - подложке. Такая структура

в сочетании с соответствующим методом формирования элементов позволяет избежать

так называемого эффекта защелкивания (тиристорного эффекта).

2.

Формирование n

и р - карманов проводят по варианту самосовмещения. На поверхность пластины

наносят двухслойную плёнку SiO2 + Si3N4, в которой путём фотолитографии вытравливают

области n –

кармана, после чего проводят имплантацию ионов фосфора с энергией, достаточной

для легирования, но недостаточной для прохождения через плёнку SiO2+Si3N4.

Рисунок 4.2 - Схема изготовления КМОП-ИМ на одной пластине с р

- карманами:

а - термическое оксидирование, первая фотолитография;

б — локальная диффузия: в - вторая фотолитография; г — локальная диффузия; д

— третья фотолитография: е — локальная диффузия; ж — четвертая

фотолитография; з — выращивание тонкого подзатворного оксида и пятая

фотолитография; и — формирование затворов и металлизации

При

постимплантационном термическом окислении n - кармана на поверхности

открытых областей происходит рост окисла, тогда как остальная часть подложки,

защищённая слоем Si3N4, не окисляется. Затем методом селективного травления удаляют слой

Si3N4 и во вновь открытых

областях подложки формируют p - карман имплантацией ионов бора. Бор проникает в подложку

через тонкую пленку Si02, в то время как области n-карманов защищены более

толстым слоем окисла. После имплантации весь окисел удаляют и проводят

диффузионную разгонку примеси в карманах.

3.

Для изоляции транзисторов в КМОП - технологии можно использовать метод LOCOS, однако особенностью

является необходимость изоляции двух различных типов транзисторов,

локализованных в различных карманах вблизи границы их соприкосновения. Для

того, чтобы удержать пороговые напряжения возникающих при этом паразитных

транзисторов на высоком уровне, необходимо размещать n - и р - канальные

транзисторы довольно далеко от границы кармана.

4.

Особенностью регулировки порогового напряжения в КМОП - технологии является то,

что величина Um должна быть почти одинаковой для обоих типов

транзисторов и составлять менее 1 В. Однако если для различных транзисторов

использовать затвор одного типа (высоколегированный поликристаллический кремний

-типа), то разность работ выхода

электронов будет отличаться для р- и n-канальных транзисторов, что приводит к асимметрии пороговых

напряжений обоих типов транзисторов. Подлегирование бором канала в р -

кармане уменьшает величину Uпор. Наоборот, подлегирование бором канала в n - канальном транзисторе

увеличивает величину Uпор. Таким образом при соответствующем выборе уровня

легирования р - и n - областей можно использовать только один неселективный (без

дополнительной фотолитографии) процесс ионной имплантации бора для управления

(сближения) величин Uпор каждого типа транзистора.

-типа), то разность работ выхода

электронов будет отличаться для р- и n-канальных транзисторов, что приводит к асимметрии пороговых

напряжений обоих типов транзисторов. Подлегирование бором канала в р -

кармане уменьшает величину Uпор. Наоборот, подлегирование бором канала в n - канальном транзисторе

увеличивает величину Uпор. Таким образом при соответствующем выборе уровня

легирования р - и n - областей можно использовать только один неселективный (без

дополнительной фотолитографии) процесс ионной имплантации бора для управления

(сближения) величин Uпор каждого типа транзистора.

На

последующих этапах проводят осаждение n+ - поликремния и формирование затворов.

5.

Ионная имплантация областей истока и стока. Для уменьшения числа

фотолитографий сначала проводят имплантацию бора без маскирования в истоки и

стоки как n -,

так и р - канальных транзисторов.

Затем локально, после проведения фотолитографии,

выполняют ионную имплантацию фосфора в области истока и стока n - канальных транзисторов

с более высокой дозой, достаточной для перекомпенсации находящегося там бора.

На заключительных этапах формирования КМОП СБИС

производят осаждение на поверхность фосфорно-силикатного стекла и его плавление

при высокой температуре. После вскрытия окон в слое ФСС формируют металлизацию.

Наконец, самым последним слоем наносят слой плазмохимического нитрида кремния,

который обеспечивает герметизацию приборов и их защиту от механических

повреждений [2, 5].

5 Особенности

субмикронных МОП – транзисторов

Традиционная структура МОП - транзистора

обеспечила снижение длины затвора от 10 мкм в 70-х годах до 0,06 мкм в настоящее

время путём простого масштабирования, то есть уменьшением длины затвора,

толщины диэлектрика и глубины залегания p-n-переходов. Однако

переход проектных норм через границу 130 нм в рамках традиционной конструкции

наталкивается на физические ограничения. Таким образом, транзисторы для

технологий XXI века должны иметь иную структуру и использовать новые материалы

для подзатворного диэлектрика.

Таблица 5.2.

Ограничения дальнейшей миниатюризации

Характеристики Предел Причина

ограничения

Толщина

окисла 2,3 нм Туннелирование через

окисел

Глубина

p-n-переходов 30 нм Сопротивление областей истока и стока

Легирование канала Vt = 0,25 В* Подпороговый ток

Мелкие

области истока и стока 15 нм Сопротивление

Длина

канала 60 нм Подпороговый ток

Длина

затвора 100 нм Подпороговый ток

*) Vt - пороговое напряжение.

С уменьшением геометрических размеров

транзисторов снижается площадь кристалла, уменьшаются паразитные ёмкости,

улучшается быстродействие и снижается энергопотребление СБИС. За последние 30

лет длина затвора МОП -транзистора уменьшилась в 200 раз (с 10 мкм в начале

70-х годов до 60 нм в наши дни). В настоящее время коммерчески доступной

является технология с минимальными горизонтальными размерами элементов 0,13

мкм, позволившая реализовать массовое производство микропроцессоров Intel Pentium 4 с тактовой частотой

более 2,5 ГГц на МОП - транзисторах с длиной канала 60 нм и толщиной

подзатворного окисла 1,5 нм. В соответствии с прогнозами Ассоциации предприятий

полупроводниковой индустрии NTRS, минимальные размеры элементов будут продолжать

быстро уменьшаться и к 2012 году достигнут 50 нм.

Каждый технологический шаг в направлении

уменьшения размеров сопряжён с ростом проблем конструирования и производства, которые

приходится решать для обеспечения теоретически прогнозируемых характеристик

транзистора. Любое улучшение одних параметров приводит к ухудшению других,

причём с уменьшением размеров взаимное влияние параметров становится всё более

сильным.

С ростом степени интеграции СБИС и систем на

кристалле увеличивается доля чипов, содержащих аналоговые блоки, которые

обеспечивают взаимодействие с окружающим миром, необходимое для крупных и

функционально законченных систем. К транзисторам для аналоговых и цифровых

применений предъявляются противоречивые требования. Для цифровых СБИС пороговое

напряжение нельзя снижать неограниченно, поскольку при этом увеличивается

подпороговый ток, который определяет потребление энергии СБИС в неактивном

состоянии. Верхний предел порогового напряжения ограничивается четвертью от

напряжения питания, которое стараются снизить для уменьшения потребляемой

мощности. Однако для аналоговых схем идеальным является нулевое пороговое

напряжение Vt = 0, что увеличивает динамический диапазон аналоговой схемы,

определяемый разностью между напряжением на затворе и Vt, то есть (Vgs – Vt).

Особыми требованиями к "аналоговым"

транзисторам являются также повышенная нагрузочная способность (ток стока в

режиме насыщения), линейность и малые нелинейные искажения на малом сигнале.

Для дифференциальных каскадов и токового зеркала важна согласованность

характеристик транзисторов.

Основными проблемами микроминиатюризации МОП - транзисторов

являются туннелирование через затвор, инжекция горячих носителей в окисел,

прокол между истоком и стоком, утечки в подпороговой области, уменьшение

подвижности носителей в канале, увеличение последовательного сопротивления

между истоком и стоком, обеспечение запаса между пороговым напряжением и

напряжением питания. Транзистор должен иметь слабую зависимость порогового

напряжения от напряжения на стоке, от длины и ширины канала, а также большую

передаточную проводимость, большое выходное сопротивление, малое сопротивления

областей истока и стока и большую нагрузочную способность. Емкости затвора и p-n-переходов должны быть

минимальны. Разброс параметров техпроцесса, который растёт с уменьшением

размеров транзистора, не должен снижать процент выхода годных кристаллов.

5.1 Конструкции МОП -

транзисторов в СБИС

Наиболее распространённой конструкцией МОП - транзистора,

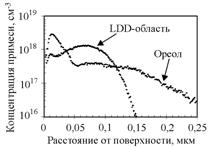

используемой более 10 лет в полупроводниковой промышленности, является LDD (Lightly Doped Drain) структура (рисyнок 5.1). Её особенностью

является наличие мелких слаболегированных областей, которые удлиняют области

истока и стока в сторону канала. Концентрацию легирующей примеси в этих

областях (фосфор и бор) и режим её разгонки выбирают таким образом, чтобы

получить плавный p-n-переход.

Обычно концентрация примеси составляет от  до

до  , в то время как в n± областях она достигает

, в то время как в n± областях она достигает –

–  .

Полученное таким способом снижение напряжённости электрического поля в канале

на границе со стоком уменьшает энергию горячих электронов, которые вызывают

долговременную деградацию параметров транзистора.

.

Полученное таким способом снижение напряжённости электрического поля в канале

на границе со стоком уменьшает энергию горячих электронов, которые вызывают

долговременную деградацию параметров транзистора.

Рисунок 5.1 - Типовая структура МОП - транзистора.

Пунктиром показан ореол (halo), охватывающий LDD-области истока и стока

Слаболегированные LDD-области также повышают

напряжение прокола, инжекционного и лавинного пробоя транзистора, уменьшают DIBL-эффект и эффект

модуляции длины канала.

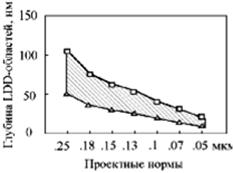

Глубина LDD-областей истока и стока составляет

50–100 нм для транзисторов с длиной канала 0,25 мкм (рис. 5.2, табл. 5.1).

Уменьшение глубины p-n-переходов до 10 нм приводит к увеличению сопротивления

слоёв истока и стока до 10 кОм/квадрат, что ограничивает нагрузочную

способность транзистора. Перекрытие LDD-областей затвором должно быть не менее

15–20 нм, чтобы предотвратить снижение нагрузочной способности транзистора.

Толщина поликремниевого затвора составляет порядка 300 нм.

Таблица

5.1 Масштабирование МОП - транзисторов согласно NTRS

Проектные

нормы, нм 250 180 130 100

70

Толщина

окисла, нм 4–5 3–4 2–3 1,5–2 <1,5

Глубина

p-n-переходов, нм 50–100 36–72 26–52 20–40 15–30

Напряжение

питания, В 1,8–2,5 1,5–1,8 1,2–1,5 0,9–1,2 0,6–0,9

Ток

утечки, нА/мкм 1 1 3 3

10

Рисунок 5.2 - Уменьшение глубины залегания

p-n-переходов LDD-областей истока и стока с развитием технологии

Для снижения емкостей транзистора выбирают

слаболегированную подложку, а для обеспечения необходимого порогового

напряжения и снижения напряжения прокола применяют легирование канала примесью

того же типа, что и в подложке. Легирование выполняют примерно на глубину

области пространственного заряда под затвором.

Контакты к областям истока, стока и к

поликремниевому затвору выполняют с промежуточным формированием слоя TiSi2

или CoSi2 толщиной порядка 40 нм, что обеспечивает удельное

сопротивление около 5 Ом на квадрат. Изоляция между поликремниевым затвором и

контактами к истоку и стоку выполняется в виде спейсера (разграничителя) (рис. 5.1)

из Si3N4.

Концентрация примеси в канале составляет  . Увеличение концентрации примеси свыше

этого значения, необходимое для транзисторов с длиной канала менее 100 нм, ведёт

к появлению туннелирования электронов через р - n - переходы истока и стока.

. Увеличение концентрации примеси свыше

этого значения, необходимое для транзисторов с длиной канала менее 100 нм, ведёт

к появлению туннелирования электронов через р - n - переходы истока и стока.

Толщина окисла для транзисторов с длиной канала

0,1 мкм составляет 3–4 нм. Между толщиной окисла tox и длиной канала

L МОП – транзисторов, изготавливаемых фирмой Intel в течение последних 20 лет,

существует эмпирическая зависимость L = 45·tox.

Для формирования карманов МОП - транзисторов

разного типа проводимости (рис. 5.3) используют фосфор и бор. Изоляцию между

карманами выполняют обычно мелкими канавками, стенки которых окисляют, а

внутренность заполняют поликремнием. Эта технология изоляции стала доминирующей

в транзисторах, выполненных по 0,25-микронной технологии и пришла на смену

изоляции локальным окислением кремния (LOCOS).

Рисунок 5.3 - Комплиментарная пара транзисторов,

использованная в 0,25-мкм техпроцессе при производстве микропроцессоров Intel®

Celeron и Pentium® II

5.2 Методы улучшения

характеристик МОП - транзисторов

Уменьшение порогового напряжения при снижении

длины канала является индикатором появления короткоканальных эффектов при

разработке новых технологий и одновременно существенным препятствием на пути

сокращения размеров транзисторных структур. Для борьбы с эффектами короткого

канала используется изменение профиля легирующей примеси как в горизонтальном,

так и в вертикальном направлении. В горизонтальном направлении (вдоль канала)

создают ореол (halo) вокруг слаболегированных областей истока и стока (рис. 5.1),

выполняют ионную имплантацию в кармашки (pockets). В вертикальном направлении

создают неоднородное (ретроградное) распределение примеси, экстремально мелкие

области истока и стока, применяют новые материалы с большей, чем у окиси

кремния, диэлектрической проницаемостью.

Проникновение области обеднения стока в канал

является основной причиной появления короткоканальных эффектов. Однако их

нельзя устранить путём простого повышения концентрации легирующей примеси в

подложке, поскольку при этом растёт подпороговый ток и уменьшается подвижность

носителей в канале, вызывающая деградацию нагрузочной способности транзистора.

Наиболее распространённым решением этой проблемы является реализация так

называемого обратного эффекта короткого канала, когда с уменьшением длины

канала пороговое напряжение возрастает. Этого можно достичь применением ореола

(halo) вокруг областей истока и стока (рис. 5.1).

Ореол создаётся ионным легированием примеси того

же типа проводимости, что и карман (бор или индий для n-канального транзистора

и мышьяк для p-канального). Индий, по сравнению с бором, снижает крутизну

падения порогового напряжения, в зависимости от длины канала, и уменьшает

разброс наклона подпороговой характеристики. Ионное легирование может

выполняться вертикально, но чаще под углом, для чего кремниевую пластину

наклоняют на угол от 20–30 до 90 град. по отношению к ионному пучку, чтобы

направить его под затвор. Ореол делают обычно на том же этапе литографии, что и

мелкие слаболегированные области истока и стока. Энергию имплантации выбирают

достаточно большую, чтобы увеличить глубину залегания ореола. После формирования

спейсера, во время отжига областей истока и стока, имплантант диффундирует за

LDD-области, обеспечивая показанный на рис. 5.4 профиль распределения примеси.

Рисунок 5.4 - Профиль примеси в области

ореола и слаболегированной (LDD) области истока или стока для 0,25-мкм

технологии

Принцип действия ореола

основан на том, что пороговое напряжение МОП - транзистора зависит от средней

концентрации примеси под затвором, а не от её горизонтального распределения.

Поэтому введение ореола увеличивает пороговое напряжение, однако практически не

влияет на среднюю подвижность носителей в канале. Ионное легирование в кармашек

(pocket) отличается от ореола только тем, что охватывает не всю LDD-область, а

только её часть у поверхности или снизу (рис. 5.5).

Принцип действия ореола

основан на том, что пороговое напряжение МОП - транзистора зависит от средней

концентрации примеси под затвором, а не от её горизонтального распределения.

Поэтому введение ореола увеличивает пороговое напряжение, однако практически не

влияет на среднюю подвижность носителей в канале. Ионное легирование в кармашек

(pocket) отличается от ореола только тем, что охватывает не всю LDD-область, а

только её часть у поверхности или снизу (рис. 5.5).

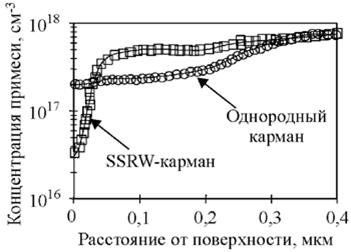

Рисунок 5.5. Крутое ретроградное распределение

примеси в кармане (SSRW)

Крутое ретроградное распределение

примеси (Super Steep Retrograde Well, SSRW) (рис. 5.5) создаётся путём

медленной диффузии мышьяка или сурьмы для р - канальных приборов и индия для

n-канальных. Благодаря возможности устанавливать поверхностную концентрацию

легирующей примеси независимо от объёмной, появляется дополнительная степень

свободы для независимой регулировки порогового напряжения и концентрации

примеси в подложке, влияющей на величину области пространственного заряда и,

соответственно, короанальные эффекты. Правильное применение идеи SSRW позволяет

ослабить влияние короткоканальных эффектов и увеличить поверхностную

подвижность носителей, однако при этом несколько увеличивается подпороговый

ток.

Сравнение структур с однородным и

ретроградным распределением примеси достаточно неоднозначно из-за сложности

выбора условий сравнения и иногда даёт противоречивые результаты.

Разновидностью крутого ретроградного распределения примеси является

дельта-легирование подложки, имеющее аналогичные свойства.

Одним из путей увеличения передаточной

проводимости и нагрузочной способности МОП - транзистора является уменьшение

толщины подзатворного окисла. Толщина окисла ограничивается появлением

паразитного туннельного тока, который увеличивает энергопотребление микросхемы,

и нестабильностью напряжения пробоя окисла, снижающей надёжность.

Экспериментально показана возможность

уменьшения толщины подзатворного диэлектрика до 1,5 нм. В эксперименте длина

канала составляла около 0,1 мкм, при этом нагрузочная способность транзистора

была равна 1 мА/мкм, передаточная проводимость — 1000 мСим/мм при комнатной

температуре.

Рост туннельного тока через окисел

является не единственной преградой на пути уменьшения его толщины. В

экспериментах с приборами, имеющими толщину затвора 1,2–2,8 нм, было показано,

что с ростом туннельного тока увеличивается статистический разброс порогового

напряжения. Это объясняется тем, что пороговое напряжение начинает зависеть от

падения напряжения на омическом сопротивлении затвора; падение напряжения

вызывается прохождением туннельного тока. При этом в разброс порогового

напряжения вносится компонента, связанная с разбросом сопротивления затвора.

Ещё одной причиной, мешающей дальнейшему

уменьшению размеров транзисторов, является квантово - механическая природа

инверсионного слоя, которая не позволяет электронам располагаться

непосредственно у поверхности кремния. Максимум пространственного распределения

электронов находится на расстоянии около 1 нм от поверхности. Это увеличивает

эффективную толщину окисла примерно на 0,3 нм. Кроме того, вследствие

ограниченной концентрации примеси в поликремниевом затворе в нём наступает

режим обеднения, из-за которого увеличивается эффективная толщина подзатворного

слоя диэлектрика. Общее увеличение эффективной толщины составляет около 0,7 нм,

что уменьшает ток стока и нагрузочную способность транзистора.

В экспериментах с приборами, имеющими

толщину окисла 1,3–1,5 нм, было обнаружено, что туннельный ток через

подзатворный диэлектрик может быть существенно уменьшен путём повышения

однородности плёнки окисла. Для получения однородной плёнки в работе

использовано селективное эпитаксиальное наращивание нелегированного кремния для

получения канала МОП - транзистора, поскольку плёнка окисла на эпитаксиально

выращенном кремнии получается более однородной. Для получения канала сначала

была выполнена ионная имплантация бора в область канала для n - канального

транзистора и фосфора для р - канального. Затем из газовой фазы был выращен

эпитаксиальный слой нелегированного кремния толщиной от 5 до 20 нм. Благодаря

предварительному легированию кремния был получен практически идеальный

ретроградный профиль примеси в эпитаксиальном слое. После этого была получена

тонкая (1,5 нм) плёнка окисла путём окисления эпитаксиального слоя в сухом

кислороде. Затвор был выполнен не из поликремния, как обычно, а из TiN.

Зернистость TiN примерно в три раза меньше, чем у поликремния, что улучшило

однородность диэлектрика под затвором.

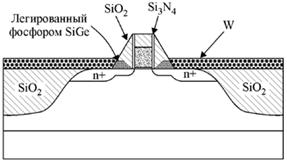

Ключевым моментом техпроцесса для длин

канала менее 100 нм является получение мелких (менее 20 нм) p-n-переходов.

Однако они дают неприемлемо высокое сопротивление областей истока и стока. Для

его снижения обычно используют промежуточный слой из TiSi2 или CoSi2,

рис. 5.6. После формирования слоя подзатворного окисла толщиной 4,6 нм

формируется поликремниевый затвор с помощью электронно-лучевой литографии.

Между затвором и областями локального окисления оставляется пространство 0,35

мкм для формирования областей истока и стока. Боковые стенки поликремниевого

затвора защищаются тонким (10–20 нм) слоем Si3N4 для

отделения затвора от контактов к истоку и стоку. После этого выполняется

селективное эпитаксиальное наращивание слоя SiGe толщиной 50 нм, легированного

фосфором. Далее формируют второй защитный слой на боковых стенках

поликремниевого затвора, который является маской для последующей имплантации

областей истока и стока. При последующей диффузии фосфора из нанесённого ранее

слоя SiGe формируются мелкие слаболегированные области истока и стока. Контакты

к истоку, стоку и затвору выполняют селективным наращиванием вольфрама.

Полученная таким образом структура показана на рис. 5.6. Часть эпитаксиального

слоя, находящаяся поверх мелких областей истока и стока, понижает их омическое

сопротивление.

Рисунок 5.6 - МОП - структура,

в которой мелкие области истока и стока получены диффузией из легированного

фосфором SiGe

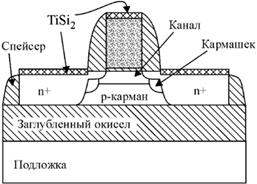

Рисунок 5.7 - КНИ – структура

с длиной канала 0,28 мкм и шириной 9,1 мкм

Список

использованных источников

1.

Интегральные схемы на МОП – приборах. Пер с англ. / Под ред. А. Н.

Карамзинского. - М. : Мир , 1975 г.

2.

А. П. Бурманов. Физические основы технологии микроэлектроники.

3.

Особенности

субмикронных МОП - транзисторов: Режим доступа: [http://www.chipinfo.ru/literature/chipnews/200207/4.html]

4.

Р. Мелен, Г. Гарланд. ИС с КМОП структурами, 1979 г.

5.

И. А. Малышева. Технология производства ИС, 2002 г.

6.

Г. Я. Красников. Конструктивно – технологические особенности

субмикронных МОП – транзисторов, 2004 г.

7.

Технология СБИС. Кн. 1 и Кн. 2 : В 2 кн. / Пирс К. , Адамс А. , Кац Л.

и др. ; Под ред. Чистякова Ю. Д. - М. : Мир , 1986.

8.

Березин, Андрей Сергеевич

9.

Технология и конструирование интегральных микросхем : [учебное пособие

для вузов по спец. "Физика и технология материалов и компонентов электрон.

техники" и "Микроэлектроника и полупроводниковые приборы"] /

Березин А. С., Мочалкина О. Р. - М. : Радио и связь , 1992.